## DOKUZ EYLÜL UNIVERSITY GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

# NEW POSSIBILITIES IN THE DESIGN OF ANALOG INTEGRATED CIRCUIT WITH MOS-C REALIZATION

by Ahmet GÖKÇEN

> June, 2010 İZMİR

# NEW POSSIBILITIES IN THE DESIGN OF ANALOG INTEGRATED CIRCUIT WITH MOS-C REALIZATION

A Thesis Submitted to the

Graduate School of Natural and Applied Sciences of Dokuz Eylül University

In Partial Fulfillment of the Requirements for the Degree of Doctor of

Philosophy in Electrical and Electronics Engineering,

Electrical and Electronics Program

by

Ahmet GÖKÇEN

June, 2010 İZMİR

#### Ph.D. THESIS EXAMINATION RESULT FORM

We have read the thesis entitled "NEW POSSIBILITIES IN THE DESIGN OF ANALOG INTEGRATED CIRCUIT WITH MOS-C REALIZATION" completed by AHMET GÖKÇEN under supervision of PROF.DR. UĞUR ÇAM and we certify that in our opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Doctor of Philosophy.

| Supervis                   | or                          |

|----------------------------|-----------------------------|

| Prof. Dr. Haldun KARACA    | Prof. Dr. Erol UYAR         |

| Thesis Committee Member    | Thesis Committee Member     |

| Doç. Dr. A. Tahsin TOLA    | Yrd. Doç. Dr. Selçuk KILINÇ |

| Examining Committee Member | Examining Committee Member  |

Prof.Dr. Mustafa SABUNCU

Director

Graduate School of Natural and Applied Sciences

#### ACKNOWLEDGMENTS

First and foremost, I express my deepest gratitude to my advisor Prof. Dr. Uğur ÇAM for his guidance, support, and advices at every stage of this dissertation. It has been a great honor and privilege for me to work with Prof. Dr. ÇAM. His valuable insights, experiences, and encouragement will guide me in all aspects of my academic life in the future.

I would like to thank the member of my Thesis Progress Committee Dr. Haldun KARACA, for useful comments, trust and support.

I would like to thank the member of my Thesis Progress Committee Dr. Erol UYAR for his useful comments and suggestions.

I would like to thank Dr. Selçuk KILINÇ for his useful comments and suggestions.

I am also thankful to my kind friends Yakup KUTLU, Umut DENİZ, Şebnem SEÇKİN, Tarık SERİNDAĞ, Güven İPEKOĞLU, and my other dear friends who I could not write here for their helps, supports and warmest friendships throughout PhD studies.

I am also grateful to my love, Sevil SAHİLLİOĞLU because without her encouragement, suggestions, contributions and patience this study would not be possible.

Finally, with great pride, I would like to express my deep appreciation and gratitude to my family who gave me both material and spiritual support throughout my university education without expecting anything in return except for my success and health. They have been really understanding and patient. I love them all.

Ahmet GÖKÇEN

## NEW POSSIBILITIES IN THE DESIGN OF ANALOG INTEGRATED CIRCUIT WITH MOS-C REALIZATION

#### **ABSTRACT**

In this thesis, MOS-C realization approach in analog integrated circuits is investigated. According to this approach, resistors in a circuit are implemented by MOS transistors. For this purpose, firstly the nonlinearity cancellation techniques in the MOS transistor currents are examined and the relevant equations are presented. Appropriate active elements, namely operational amplifier, operational transresistance amplifier, first generation current conveyor, second generation current conveyor, third generation current conveyor, inverting second generation curret conveyor, differential voltage current conveyor, differential difference current conveyor, for the nonlinearity cancellation techniques are given, also the element representations and the terminal equations are shown. Using the nonlinearity cancellation techniques and above mentioned active elements, two new first order allpass filters are presented. Kerwin-Huelsman-Newcomb, Fleischer-Tow and Tow-Thomas biquads are improved for fully integrable and electronically tunable property. A novel single amplifier biquad is obtained and an oscillator circuit is modified for tunable oscillation frequency. As an application example, fifth order elliptic video filter is given. In all of the above mentioned circuits, the resistors are implemented via MOS transistors and this feature gives them fully integrable property. By changing the gate voltage of the MOS transistor, the circuit parameters have electronically tunable feature. The natural frequency, the quality factor and the gain of the circuits can be changed electronically. The workability of the presented circuits has been verified by PSPICE simulation results.

**Keywords:** Analog Integrated Circuits, MOS-C Realization, Nonlinearity Cancellation in MOS Transistor Current

### MOS-C GERÇEKLEMESİ İLE ANALOG TÜM DEVRE TASARIMINDA YENİ OLANAKLAR

ÖZ

Bu tezde, analog tümdevrelerdeki MOS-C gerçeklemesi yaklaşımı incelenmiştir. Bu yaklaşıma göre, devrelerdeki dirençler MOS tranzistörler ile gerçeklenir. Bu amaç için, ilk olarak MOS tranzistör akımındaki doğrusal olmayan terimlerin yok edilme teknikleri incelenmiş ve bu tekniklere ait denklemler verilmiştir. Bahsedilen bu tekniklerin kullanılabileceği uygun aktif eleman yapıları işlemsel kuvvetlendirici, işlemsel geçiş-direnç kuvvetlendiricisi, birinci nesil akım taşıyıcı, ikinci nesil akım taşıyıcı, üçüncü nesil akım taşıyıcı, ikinci nesil tersleyen akım taşıyıcı, diferansiyel gerilim akım taşıyıcı, diferansiyel fark akım taşıyıcı sunulmuş, terminal bağlantıları ve eleman simgeleri gösterilmiştir. Bahsedilen doğrusal olmayan terimleri yok etme tekniklerini ve bunlara uygun aktif elemanları kullanarak iki adet yeni birinci dereceden tüm geçiren süzgeç devresi tasarlanmıştır. Kerwin-Huelsman-Newcomb Fleischer-Tow ve Tow-Thomas filtre devreleri tümüyle tümleşik edilebilir ve elektronik olarak ayarlanabilir özellikte yeniden geliştirilmiştir, Yeni bir tek aktif elemanlı filtre devresi tasarlanmış ve daha önce sunulmuş olan bir osilatör devresi geliştirilerek elektronik ayarlı frekansa sahip hale getirilmiştir. Ayrıca bir uygulama devresi olarak da beşinci dereceden eliptik video filtre uygulaması sunulmuştur. Sunulan bütün devrelerdeki dirençler MOS tranzistörler ile gerçeklenmiş ve bu özellik sayesinde devreler tümdevre edilebilir hale gelmişlerdir. MOS tranzistörlerin kapı gerilimlerini değiştirerek, sunulan devrelerin açısal frekansları, kalite faktörleri ve kazançları elektronik olarak ayarlanabilir özelliğe sahip olmaktadır. Sunulan devrelerin çalışabilirliği PSPICE benzetim sonuçlarıyla gösterilmiştir.

**Anahtar Kelimeler:** Analog Tümdevreler, MOS-C Gerçeklemesi, MOS Tranzistör Akımındaki Doğrusal Olmayan Terimlerin Yok Edilmesi

### **CONTENTS**

|                                                         | Page     |

|---------------------------------------------------------|----------|

| THESIS EXAMINATION RESULT FORM                          | ii       |

| ACKNOWLEDGEMENTS                                        | iii      |

| ABSTRACT                                                | iv       |

| ÖZ                                                      | v        |

| CHAPTER ONE – INTRODUCTION                              | 1        |

| 1.1 Introductory Remarks                                | 1        |

| 1.2 Overview of the Thesis                              | 3        |

| CHAPTER TWO - MOSFET BASED RESISTOR REAL                | LIZATION |

| TECHNIQUES                                              | 5        |

|                                                         |          |

| 2.1 The MOSFET as a Voltage Controlled Resistor         |          |

| 2.2 Nonlinearity Cancellation of Transistor Current     |          |

| 2.2.1 First Technique for Nonlinearity Cancellation     | 9        |

| 2.2.2 Second Technique for Nonlinearity Cancellation    | 11       |

| 2.2.3 Third Technique for Nonlinearity Cancellation     | 13       |

| 2.2.4 Fourth Technique for Nonlinearity Cancellation    | 15       |

| 2.2.5 Fifth Technique for Nonlinearity Cancellation     | 17       |

| 2.2.6 Sixth Technique for Nonlinearity Cancellation     | 19       |

| 2.2.7 Seventh Technique for Nonlinearity Cancellation   | 21       |

| 2.2.8 Eighth Technique for Nonlinearity Cancellation    | 23       |

| 2.2.9 Ninth Technique for Nonlinearity Cancellation     | 25       |

| 2.2.10 Tenth Technique for Nonlinearity Cancellation    | 27       |

| 2.3 Comparision of Nonlinearity Cancellation Techniques | 28       |

| CHAPTER     | THREE -            | SUITABLE          | ACTIVE         | COMPONENTS           | FOR  |

|-------------|--------------------|-------------------|----------------|----------------------|------|

| NONLINEA    | ARITY CANCE        | CLLATION TE       | CHNIQUES       | ••••••               | 30   |

| 3.1 Onera   | ntional Amplifier  | •¢                |                |                      | 30   |

|             |                    |                   |                |                      |      |

|             | •                  |                   |                |                      |      |

|             | _                  |                   |                |                      |      |

|             |                    |                   |                |                      |      |

| 5.5 Opera   | uionai iransiesis  | stance Ampimer    | •••••          |                      | 39   |

|             |                    |                   |                | RITY CANCELLA        |      |

| TECHNIQU    | UES WITH INT       | TEGRATOR          | ••••••         | ••••••               | 41   |

| 4.1 Op-A    | mp Based Integr    | ator              |                |                      | 41   |

| 4.1.1 N     | Miller Integrator. |                   |                |                      | 41   |

| 4.1.2 (     | Op-Amp Integrat    | or                |                |                      | 43   |

| 4.2 OTR     | A Based Integrat   | or                |                |                      | 45   |

| 4.3 ICCII   | Based Integrato    | r                 |                |                      | 47   |

| 4.4 Perfor  | rmance Compari     | son               |                |                      | 48   |

| CHAPTER     | FIVE – MOS-C       | C REALIZATIO      | ON EXAMP       | LES                  | 50   |

| 5.1 First ( | Order Allpass Fi   | lters             |                |                      | 50   |

| 5.1.1 F     | First Topology fo  | or First Order Al | lpass Filter   |                      | 51   |

| 5.1.2 S     | Second Topology    | for First Order   | Allpass Filter |                      | 58   |

| 5.2 Single  | e Amplifier Biqu   | ad                |                |                      | 65   |

| 5.3 Fleisc  | her Tow Biquad     |                   |                |                      | 78   |

| 5.4 Kerwi   | in- Huelsman-N     | ewcomb Biquad     |                |                      | 87   |

| 5.5 Electr  | onically Variabl   | e Frequency Oso   | illator        |                      | 95   |

| 5.6 Tow-    | Thomas Biquad      | and Quadrature    | Oscillator as  | an ICCII Application | ıs98 |

| 5.6.1 T     | Tow-Thomas Bio     | ıuad              |                |                      | 98   |

| 5.6.2 (     | Quadrature Oscil   | lator             |                |                      | 102  |

| 5.7 Video Filter Application | 104 |

|------------------------------|-----|

| CHAPTER SIX – CONCLUSION     | 106 |

| 6.1 Concluding Remarks       | 106 |

| 6.2 Future Work              | 107 |

| REFERENCES                   | 108 |

| APPENDICES                   | 121 |

## CHAPTER ONE INTRODUCTION

#### 1.1 Introductory Remarks

Metal-oxide-semiconductor (MOS) technology was originally developed for digital large-scale integration (LSI) design. The small size and self-isolating nature of the enhancement-mode MOS transistors allows a much higher functional density to be achieved on an integrated circuit (IC) chip than is possible with bipolar technology. Traditionally, MOS technology has been used extensively in the design of wholly digital system blocks, such as microprocessors and memories. On the other hand, analog circuit functions, such as amplifiers, digital to analog converters, and active filters, have been designed primarily with bipolar technology (Grebene, 1983).

Technological progress over years has rapidly increased the feasible level of integration for complete systems containing both digital and analog functions. Thus, the dividing line between analog and digital LSI technologies has become less distinct. Therefore, it has become necessary to extend the capabilities of MOS technology into analog IC design so that a higher level of system integration can be made economically feasible (Grebene, 1983).

The use of MOS transistors to perform analog functions presents many design challenges and requires a number of design compromises. In most cases, the resulting MOS analog blocks, such as operational amplifiers (op-amps), comparators, or voltage references, may not be able to meet the performance specifications of their bipolar equivalents, but still perform satisfactorily as a subsystem within the monolithic chip. The high density of MOS transistors makes it possible to integrate analog functions on a much smaller chip area. For example, a MOS op-amp requires only 30-50% of the chip area that is needed for an equivalent bipolar amplifier. The usage of MOS makes it possible to increase greatly the density of analog functions on the chip (Gray, Hurst, Lewis & Meyer, 2000).

Automatic electronic tuning is crucial for fully integrated filters to compensate the drifts of element values and filter performances due to component tolerance, device non-ideality, parasitic effects, temperature, environment and aging.

In conventional active RC filters in ICs, the resistor is the problem; it has a very limited range of values (normally  $R \leq 40 k\Omega$  without use of special processing techniques and resistances beyond the limit will be physically too large) and is not electronically tunable.

On the other hand, a MOSFET can be used as a voltage-controlled resistor biased in the ohmic region, with the resistance being adjustable by the bias gate voltage. It is therefore obvious that using the MOSFET to replace the resistor in active RC filters can meet the two requirements, which are electronic tunability and occupying less area, and the resulting filters are called the MOSFET-C filters (Deliyannis, Sun & Fidler, 1999).

MOS transistors, when used in filter applications with the aim of implementing linear resistors, suffer from non-idealities causing signal distortion: body effect, mobility variation, device mismatch. These effects cause nonlinear terms in transistor current. The main object is to eliminate these nonlinear terms. In the literature, several techniques are presented to cancel these nonlinear terms. Balanced two-transistor configurations have first been introduced to cancel out even order nonlinearities (Banu & Tsividis, 1983). It was later demonstrated using a strong-inversion MOS model that a four-transistor structure fully suppresses the body effect-related odd-order terms as well (Song, 1986, Czarnul, 1986). Another technique, which uses two depletion type MOS transistors, is introduced by Babanezhad & Temes, (1984). Tsividis, Banu & Khoury, (1986) gives eight nonlinearity cancellation techniques which include above mentioned techniques. Another technique for cancelling even and odd order nonlinearities in two-MOS transistor is introduced by Ismail & Fiez (1994) and Salama & Soliman (1999a).

In the literature, a great deal of filters, oscillators, integrators and other circuits exist using these nonlinearity cancellation techniques. MOSFET-C filters are proposed by Ismail, Smith & Beale (1988), Tsividis & Shi (1985), Salama & Soliman (1999a), Salama (2002), Liu, Tsao & Wu (1990), Ibrahim & Kuntman (2004), Hwang, Chen & Lee (2005), Mahmoud & Soliman (1999), Salama, Elwan & Soliman (2001), Schmid & Moschytz (1997), Chen, Tsao & Liu (2001), Hwang, Wu, Chen, Shih & Chou (2007), Fangxiong, Min, Heping, Hailong, Yin & Forster (2009), Hwang, Wu, Chen, Shih & Chou (2009). Salama & Soliman (1999a) is proposed filter and oscillator topologies. The resistors are implemented via two NMOS transistors. Also, Salama (2002) proposed a universal filter topology using resistor implementing technique with two NMOS transistor. The filter parameters can be controlled via NMOS gate voltages. Liu, Tsao & Wu (1990) and Hwang, Chen & Lee (2005) are proposed electronically controllable filter topologies. The resistors are implemented via four NMOS transistors. Oscillators, integrators, frequency depended negative resistor and equalizer circuits are proposed by Lee (2003), Osa & Carlosena (2000), Salama & Soliman (1999c), Jia & Chen (1995), Babanezhad & Temes (1984), Chiu, Tsay, Liu, Tsao & Chen (1995), Karaca, Metin & Kuntman (2010), Sakurai, Ismail, Michel, Sinenco & Brannen (1992). Osa & Carlosena (2000) and Lee (2003) proposed electronically tunable oscillation frequency oscillator. Four NMOS are used for implementing resistors. Babanezhad & Temes (1984) proposed integrated amplifier using op-amp and grounded resistor implementing technique via depletion type two NMOS transistors.

#### 1.2 Overview of the Thesis

The main purpose of this thesis is to gain the knowledge of MOS-C realization approach in analog integrated circuit and to present new MOS-C based circuits.

This thesis is organized as follows. In Chapter 2, the implementation of resistors using MOS transistors and nonlinearity cancellation techniques are presented. For each technique, the linear and nonlinear terms are calculated and the resistor values are given.

In Chapter 3, suitable active components namely op-amp, operational transresistance amplifier (OTRA), first generation current conveyor (CCI), second generation current conveyor (CCII), third generation current conveyor (CCIII), inverting second generation curret conveyor (ICCII), differential voltage current conveyor (DVCC), differential difference current conveyor (DDCC) in IC technology for nonlinearity cancellation techniques are presented. The historical background, block diagram and terminal port relations of the components are given.

In Chapter 4, the performance comparison of four nonlinearity cancellation techniques is done by appling them on the integrator circuit. Frequency, transient and Total Harmonic Distortion (THD) analyses are presented in this chapter.

The MOS-C based allpass filter, biquadratic filter and oscillator circuit examples, and PSPICE simulation results are given in Chapter 5. All of the above mentioned circuits have electronically tunable feature and this property allows controllable center frequency, quality factor, and gain. And a fifth order video band elliptic filter topology, as the application example, is presented.

Finally, in Chapter 6, the conclusions are drawn and possible future works are given.

#### **CHAPTER TWO**

#### MOSFET BASED RESISTOR REALIZATION TECHNIQUES

IC design becomes more popular with the advances in analog VLSI technology. Resistors are one of the components in ICs, which can be designed and fabricated using semiconductor manufacturing process. Resistors fabricated in IC's physically occupy large chip areas. They have large parasitic capacitance, and that limits their applications for high frequency circuits. Resistor synthesis by using MOS transistors can result large resistance values, and they use smaller fraction of chip areas. It is important to reduce the area of the integrated circuits. In this respect, it could be attractive to implement the resistors using transistors which would reduce the size considerably. Also transistors consume less power than resistors and resistors suffer from heat effect. However, implementing resistors via MOS transistors yields linear and nonlinear terms in transistor current. The main problem is cancelling these nonlinear terms in the transistor current. In this chapter, the implementation of resistors using MOS transistors and ten nonlinearity cancellation techniques are presented. The linear and the nonlinear terms of the transistor currents are presented. The required equations are given. Also the comparisons of the techniques are given in a table.

#### 2.1 The MOSFET as a Voltage Controlled Resistor

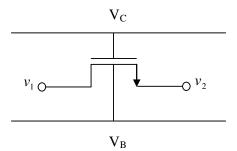

An n-channel MOSFET is shown in Figure 2.1. The device's gate is connected to a dc control voltage  $V_C$  and the substrate is connected to a fixed dc bias  $V_B$  (Tsividis, Banu & Khoury, 1986).

Figure 2.1 An n-channel MOSFET

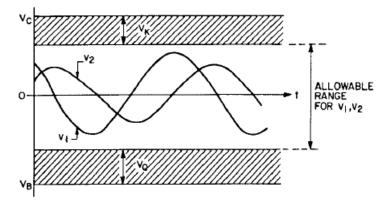

To allow operation in the "non-saturation" region, the terminal voltages  $v_1$  and  $v_2$  are assumed to remain below  $V_C$  by at least an amount  $V_K$  as shown in Figure 2.2. Also,  $v_1$  and  $v_2$  are assumed to remain above  $V_B$  by a non-critical quantity  $V_Q$  (Tsividis, Banu & Khoury, 1986).

Figure 2.2 Terminal voltages for the transistor (Tsividis, Banu & Khoury, 1986)

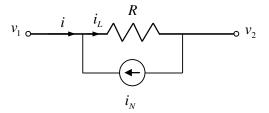

A model for the MOS transistor is shown in Figure 2.3.

Figure 2.3 Low frequency large signal model for the MOS transistor

The transistor current i can be written in the following form;

$$i = i_L - i_N \,, \tag{2.1}$$

where,  $i_N$  and  $i_L$  represent nonlinear and linear terms, respectively.

The linear term of the transistor current can be defined as follows;

$$i_L = G(v_1 - v_2). (2.2)$$

In Equation (2.2), the conductance parameter G is given by;

$$G = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_T\right). \tag{2.3}$$

where W and L are the channel width and length, respectively,  $\mu$  is the effective mobility,  $C_{ox}$  is the oxide capacitance per unit area,  $V_T$  is the threshold voltage of the transistor. Clearly, if one cancels the effect of the  $i_N$ , the transistor behaves like a linear resistor with a conductance G. The resistance  $R = \frac{1}{G}$  can be written in the following form;

$$R = \left(\frac{L}{W}\right) R_{S}, \tag{2.4}$$

where L/W is aspect ratio of the transistor, which is a design parameter, and  $R_S$  is given by;

$$R_{S} = \frac{1}{\mu C_{ox} (V_{C} - V_{T})}.$$

(2.5)

The above material holds also for p-channel devices, with appropriate changes in the signs of voltages and currents.

The nonlinear term in Equation (2.1) can be written in the following form;

$$i_{N} = g(v_{1}) - g(v_{2}), \tag{2.6}$$

where the function g(v) is independent of  $V_C$  and it can be written as;

$$g(v) = g_{e}(v) + g_{o}(v),$$

(2.7)

where  $g_e(v)$  and  $g_o(v)$  are even and odd functions, respectively, and can be expressed by;

$$g_{e}(v) = \left(\frac{W}{L}\right)\mu C_{ox} \left\{ \frac{1}{2}v^{2} + \frac{1}{3}\gamma \left[ (V_{R} + v)^{\frac{3}{2}} + (V_{R} - v)^{\frac{3}{2}} \right] \right\}, \tag{2.8}$$

$$g_{o}(v) = \left(\frac{W}{L}\right) \mu C_{ox} \left\{ \gamma \left[ \frac{1}{3} (V_{R} + v)^{\frac{3}{2}} - \frac{1}{3} (V_{R} - v)^{\frac{3}{2}} - V_{R}^{\frac{1}{2}} v \right] \right\}, \tag{2.9}$$

where  $\gamma$  is body effect coefficient and  $V_R = \phi_B - V_B$ .

The nonlinear term of the current i can be written using Equation (2.6) and (2.7) in the following form;

$$i_N = g_a(v_1) + g_a(v_1) - g_a(v_2) - g_a(v_2), \qquad (2.10)$$

$$i_{N} = [g_{e}(v_{1}) - g_{e}(v_{2})] + [g_{o}(v_{1}) - g_{o}(v_{2})].$$

(2.11)

The nonlinear term is;

$$i_{N} = \begin{bmatrix} \left[ \frac{W}{L} \right] \mu C_{ox} \begin{cases} \frac{1}{2} v_{1}^{2} + \frac{1}{3} \gamma (V_{R} + v_{1})^{\frac{3}{2}} + \frac{1}{3} \gamma (V_{R} - v_{1})^{\frac{3}{2}} \end{cases} \\ - \left\{ \frac{1}{2} v_{2}^{2} + \frac{1}{3} \gamma (V_{R} + v_{2})^{\frac{3}{2}} + \frac{1}{3} \gamma (V_{R} - v_{2})^{\frac{3}{2}} \right\} \\ + \left[ \left( \frac{W}{L} \right) \mu C_{ox} \begin{cases} \frac{1}{3} \gamma (V_{R} + v_{1})^{\frac{3}{2}} - \frac{1}{3} \gamma (V_{R} - v_{1})^{\frac{3}{2}} - \mathcal{W}_{R}^{\frac{1}{2}} v_{1} \right\} \\ - \left\{ \frac{1}{3} \gamma (V_{R} + v_{2})^{\frac{3}{2}} - \frac{1}{3} \gamma (V_{R} - v_{2})^{\frac{3}{2}} - \mathcal{W}_{R}^{\frac{1}{2}} v_{2} \right\} \end{bmatrix} \end{bmatrix}$$

(2.12)

After the simplification of the Equation (2.12),  $i_N$  is;

$$i_{N} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_{1}^{2} - v_{2}^{2}\right) + \frac{2}{3} \gamma \left(V_{R} + v_{1}\right)^{\frac{3}{2}} - \frac{2}{3} \gamma \left(V_{R} + v_{2}\right)^{\frac{3}{2}} - W_{R}^{\frac{1}{2}} \left(v_{1} - v_{2}\right)\right].$$

(2.13)

The nonlinear current of transistor includes even  $[g_e(v_1) - g_e(v_2)]$  and odd  $[g_o(v_1) - g_o(v_2)]$  components of expression. The term  $[g_e(v_1) - g_e(v_2)]$  is very small compared to the linear term  $i_L$ . The term  $[g_o(v_1) - g_o(v_2)]$  depending on  $v_1$  and  $v_2$ , can be large and its effect must be eliminated. Also, by connecting substrate to source, the body effect coefficient is zero, so the odd nonlinearities have been eliminated.

#### 2.2 Nonlinearity Cancellation of Transistor Current

Many different techniques have been proposed for eliminating the effect of nonlinearities. Some cancel the nonlinearities in the current of one device; others cancel the nonlinearities in the difference or sum of the currents in two or more devices. In all cases except for the seventh nonlinearity cancellation technique given in the following, the substrate is assumed to be connected  $V_B$ . In the seventh nonlinearity cancellation technique, p-channel device is used and the p-channel device's substrate is connected to the opposite  $V_B$  (Tsividis, Banu & Khoury, 1986).

#### 2.2.1 First Technique for Nonlinearity Cancellation

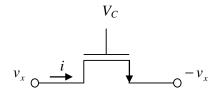

This technique uses an NMOS transistor, which operates in non-saturation region. Drain and source of the NMOS transistor is connected to equal but opposite voltages as shown in Figure 2.4. The substrate is assumed to be connected to the source, so the body effect is neglected.

Figure 2.4 The first nonlinearity cancellation technique

The transistor current i can be written as;  $i = i_L - i_N$ .  $i_L$  and  $i_N$  had been calculated previously in Equations (2.2) and (2.13). For the first nonlinearity cancellation technique,  $i_N$  and  $i_L$  are defined as;

$$i_{N} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{2}{3} \gamma (V_{R} + v_{x})^{\frac{3}{2}} - \frac{2}{3} \gamma (V_{R} - v_{x})^{\frac{3}{2}} - \gamma V_{R}^{\frac{1}{2}} 2v_{x}\right], \tag{2.14}$$

$$i_L = \left(\frac{W}{L}\right) \mu C_{ox} (V_C - V_T) 2v_x, \qquad (2.15)$$

$V_T$  is the threshold voltage of the transistor defined as;

$$V_T = V_{ER} + \phi_R + W_R^{1/2}, \tag{2.16}$$

where  $V_{FB}$  is flat-band voltage and  $\phi_B$  is the surface inversion potential. The transistor current i can be written as;

$$i = \left(\frac{W}{L}\right)\mu C_{ox} \left\{ \left\{ \left(V_C - V_{FB} - \phi_B\right) \left(2v_x\right)\right\} - \frac{2}{3}\gamma \left[\left(V_R + v_x\right)^{\frac{3}{2}} - \left(V_R - v_x\right)^{\frac{3}{2}} - V_R^{\frac{1}{2}} 2v_x\right] \right\},$$

(2.17)

by neglecting nonlinear terms, Equation (2.18) is obtained.

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_{FB} - \phi_B\right) \left(2v_x\right). \tag{2.18}$$

The resistance value of the transistor can be calculated as the following form;

$$R = \frac{2v_x}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox} \left(V_C - V_{FB} - \phi_B\right)},$$

(2.19)

$$R = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}\left(V_C - V_T\right)}.$$

(2.20)

By using this scheme, the even nonlinearities are eliminated. For zero body effect coefficient, the remaining odd nonlinearities are eliminated completely.

#### 2.2.2 Second Technique for Nonlinearity Cancellation

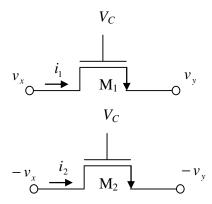

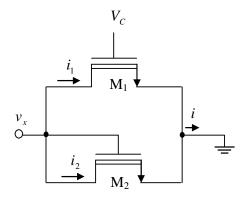

In this technique, two NMOS transistors are used, each drain and source terminals of which is connected to equal but opposite voltages, as shown in Figure 2.5.

Figure 2.5 The second nonlinearity cancellation technique

The currents of the transistors are;

$$i_1 - i_2 = [i_{L1} - i_{L2}] - [i_{N1} - i_{N2}].$$

(2.21)

Both nonlinear and linear terms can be written in the following form;

$$i_{N1} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_x^2 - v_y^2\right) + \frac{2}{3} \gamma \left(V_R + v_x\right)^{\frac{3}{2}} - \frac{2}{3} \gamma \left(V_R + v_y\right)^{\frac{3}{2}} - \mathcal{W}_R^{\frac{1}{2}} \left(v_x - v_y\right)\right].$$

(2.22)

$$i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{1}{2} \left( (-v_x)^2 - (-v_y)^2 \right) + \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} \\ -\frac{2}{3} \gamma (V_R - v_y)^{\frac{3}{2}} - W_R^{\frac{1}{2}} \left( -v_x + v_y \right) \end{bmatrix}. \tag{2.23}$$

$$i_{L1} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_T\right) \left(v_x - v_y\right). \tag{2.24}$$

$$i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} (V_C - V_T) ((-v_x) - (-v_y)). \tag{2.25}$$

Nonlinear term of the current  $i_1 - i_2$  can be written in the following form;

$$i_{N1} - i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{2}{3} \gamma (V_R + v_x)^{\frac{3}{2}} - \frac{2}{3} \gamma (V_R + v_y)^{\frac{3}{2}} - \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} \\ + \frac{2}{3} \gamma (V_R - v_y)^{\frac{3}{2}} - 2 \gamma V_R V_R^{\frac{1}{2}} (v_x - v_y) \end{bmatrix} . (2.26)$$

At the same time, linear term of the current  $i_1 - i_2$  can be written in the following form;

$$i_{L1} - i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} (V_C - V_T) 2(v_x - v_y).$$

(2.27)

Thus, current  $i_1 - i_2$  is obtained as;

$$i_{1} - i_{2} = \left[ \left( \frac{W}{L} \right) \mu C_{ox} (V_{C} - V_{T}) 2(v_{x} - v_{y}) - \left( \frac{W}{L} \right) \mu C_{ox} \left[ \frac{2}{3} \gamma (V_{R} + v_{x})^{\frac{3}{2}} - \frac{2}{3} \gamma (V_{R} + v_{y})^{\frac{3}{2}} - \frac{2}{3} \gamma (V_{R} - v_{y})^{\frac{3}{2}} + \frac{2}{3} \gamma (V_{R} - v_{y})^{\frac{3}{2}} \right] - 2 \gamma W_{R}^{\frac{1}{2}} (v_{x} - v_{y})$$

$$(2.28)$$

Because the body effect coefficient is zero, the nonlinear terms can be neglected, then the transistor current becomes as;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_T\right) 2 \left(v_x - v_y\right). \tag{2.29}$$

Thus, the resistance value of the NMOS transistors is obtained as;

$$R = \frac{2(v_x - v_y)}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_C - V_{FB} - \phi_B)} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_C - V_T)}.$$

(2.30)

Similarly, as mentioned in the first nonlinearity cancellation technique, using this scheme, the even nonlinearities and the remaining odd nonlinearities are eliminated completely.

#### 2.2.3 Third Technique for Nonlinearity Cancellation

This technique is similar to the second nonlinearity cancellation technique. Only difference is, the source terminals of both NMOS transistors are connected to the same voltage as depicted in Figure 2.6.

Figure 2.6 The third nonlinearity cancellation technique

Nonlinear and linear terms can be defined as the following form;

$$i_{N1} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_x^2 - v_y^2\right) + \frac{2}{3} \gamma \left(V_R + v_x\right)^{\frac{3}{2}} - \frac{2}{3} \gamma \left(V_R + v_y\right)^{\frac{3}{2}} - \gamma V_R^{\frac{1}{2}} \left(v_x - v_y\right)\right].$$

(2.31)

$$i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{1}{2} \left( (-v_x)^2 - (v_y)^2 \right) + \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} \\ -\frac{2}{3} \gamma (V_R + v_y)^{\frac{3}{2}} - W_R^{\frac{1}{2}} \left( -v_x - v_y \right) \end{bmatrix}. \quad (2.32)$$

$$i_{L1} = \left(\frac{W}{L}\right) \mu C_{ox} (V_C - V_T) (v_x - v_y). \tag{2.33}$$

$$i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_T\right) \left(\left(-v_x\right) - \left(v_y\right)\right). \tag{2.34}$$

Nonlinear term of the current  $i_{N1} - i_{N2}$  can be calculated as the following form;

$$i_{N1} - i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{2}{3} \gamma (V_R + V_X)^{\frac{3}{2}} - \frac{2}{3} \gamma (V_R - V_X)^{\frac{3}{2}} - 2 \gamma W_R^{\frac{1}{2}} (V_X)\right]. \quad (2.35)$$

Linear term of the current  $i_{L1} - i_{L2}$  can be written as the following form;

$$i_{L1} - i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} (V_C - V_{TB}) 2(v_x).$$

(2.36)

The transistor current  $i_1 - i_2$ , which is defined as  $[i_{L1} - i_{L2}] - [i_{N1} - i_{N2}]$ , can be written as;

$$i_{1} - i_{2} = \left(\frac{W}{L}\right) \mu C_{ox} \left\{ \left(V_{C} - V_{T}\right) 2v_{x} - \left[\frac{2}{3} \gamma (V_{R} + v_{x})^{\frac{3}{2}} - \frac{2}{3} \gamma (V_{R} - v_{x})^{\frac{3}{2}} - 2 \mathcal{W}_{R}^{\frac{1}{2}} v_{x}\right] \right\}. (2.37)$$

By using this scheme, the even nonlinearities are eliminated. By neglecting nonlinear terms the resistance value can be calculated as;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_T\right) 2v_x. \tag{2.38}$$

$$R = \frac{2v_x}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_C - V_T)}.$$

(2.39)

For the body effect coefficient of zero, the remaining odd nonlinearities are eliminated completely.

#### 2.2.4 Fourth Technique for Nonlinearity Cancellation

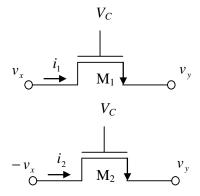

Figure 2.7 shows another nonlinearity cancellation technique. An NMOS transistor's source and drain are connected to different voltages. Also as shown in Figure 2.7, the gate is not tied to a control voltage directly as before, but instead it has voltages containing a control component  $(V'_C)$  and a signal dependent component.

Figure 2.7 The fourth nonlinearity cancellation technique

The current of the transistor is;

$$i = i_L - i_N . (2.40)$$

The nonlinear and the linear terms of the Equation (2.40) can be written as;

$$i_{N} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_{x}^{2} - v_{y}^{2}\right) + \frac{2}{3} \gamma \left(V_{R} + v_{x}\right)^{3/2} - \frac{2}{3} \gamma \left(V_{R} + v_{y}\right)^{3/2} - W_{R}^{1/2} \left(v_{x} - v_{y}\right)\right].$$

(2.41)

$$i_L = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C - V_T\right) \left(v_x - v_y\right). \tag{2.42}$$

If the control voltage of the transistor is  $V_C = V_C' + \frac{v_x + v_y}{2}$  then, linear term of the current becomes as;

$$i_{L} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{C}' + \frac{v_{x} + v_{y}}{2} - V_{T}\right) \left(v_{x} - v_{y}\right). \tag{2.43}$$

After required calculations,  $i_L$  can be calculated as;

$$i_{L} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{C}' - V_{T}\right) \left(v_{x} - v_{y}\right) + \left(\frac{v_{x}^{2} - v_{y}^{2}}{2}\right). \tag{2.44}$$

Substituting  $i_L$  and  $i_N$  in Equation (2.40), the transistor current i can be written as the following form;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left\{ (V_C' - V_T) (v_x - v_y) - \left[\frac{2}{3} \gamma (V_R + v_x)^{\frac{3}{2}} - \frac{2}{3} \gamma (V_R - v_y)^{\frac{3}{2}} + \gamma W_R^{\frac{1}{2}} (v_x - v_y)\right] \right\}.$$

(2.45)

These schemes do not eliminate even nonlinearities completely. This problem can be eliminated if a signal-dependent substrate voltage is supplied, using voltage level shifters. By neglecting nonlinear terms and body effect coefficient, the resistance value can be given by;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_C' - V_T\right) \left(v_x - v_y\right). \tag{2.46}$$

$$R = \frac{(v_x - v_y)}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_C' - V_T)}.$$

(2.47)

Due to the fact that body effect coefficient is zero, the odd nonlinearities are eliminated completely.

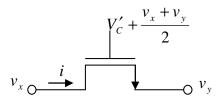

#### 2.2.5 Fifth Technique for Nonlinearity Cancellation

The fifth nonlinearity cancellation technique consists of two NMOS transistors, which are connected in parallel, as seen in Figure 2.8. The gate is not tied to a control voltage directly. The gate voltages are  $V_C = V_C' + v_y$  and  $V_C = V_C' + v_x$  for the first and the second NMOS transistors, respectively.

Figure 2.8 The fifth nonlinearity cancellation technique

The current of the transistors is equal to;

$$i_1 + i_2 = [i_{L1} + i_{L2}] - [i_{N1} + i_{N2}].$$

(2.48)

Nonlinear terms are;

$$i_{N_1} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_x^2 - v_y^2\right) + \frac{2}{3} \gamma \left(V_R + v_x\right)^{\frac{3}{2}} - \frac{2}{3} \gamma \left(V_R + v_y\right)^{\frac{3}{2}} - \gamma V_R^{\frac{1}{2}} \left(v_x - v_y\right)\right].$$

(2.49)

$$i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_{x}^{2} - v_{y}^{2}\right) + \frac{2}{3} \gamma \left(V_{R} + v_{x}\right)^{\frac{3}{2}} - \frac{2}{3} \gamma \left(V_{R} + v_{y}\right)^{\frac{3}{2}} - \mathcal{W}_{R}^{\frac{1}{2}} \left(v_{x} - v_{y}\right)\right].$$

$$(2.50)$$

$$i_{N} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\left(v_{x}^{2} - v_{y}^{2}\right) + \frac{4}{3} \gamma \left(V_{R} + v_{x}\right)^{\frac{3}{2}} - \frac{4}{3} \gamma \left(V_{R} + v_{y}\right)^{\frac{3}{2}} - 2 \mathcal{W}_{R}^{\frac{1}{2}} \left(v_{x} - v_{y}\right)\right].$$

$$(2.51)$$

Linear terms are;

$$i_{L_1} = i_{L_2} = \left(\frac{W}{L}\right) \mu C_{ox} (V_C - V_T) (v_x - v_y).$$

(2.52)

By substituting control voltage and threshold voltage, which is given in Equation (2.16) into linear terms, the following equations can be derived.

$$i_{L_1} = \left(\frac{W}{L}\right) \mu C_{ox} \left[ \left(V_C' + v_y - V_{FB} - \phi_B - \gamma (V_R)^{1/2} \right) \left(v_x - v_y\right) \right]. \tag{2.53}$$

$$i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[ \left(V_C' + v_x - V_{FB} - \phi_B - \gamma \left(V_R\right)^{1/2}\right) \left(v_x - v_y\right) \right]. \tag{2.54}$$

$$i_{L} = \left(\frac{W}{L}\right) \mu C_{ox} \left[ 2(V_{C}' - V_{FB} - \phi_{B})(v_{x} - v_{y}) + \left[ (v_{x} + v_{y})(v_{x} - v_{y}) \right] - 2\gamma (V_{R})^{\frac{1}{2}} (v_{x} - v_{y}) \right].$$

(2.55)

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left[ 2(V_C' - V_{FB} - \phi_B)(v_x - v_y) + \frac{4}{3} \gamma (V_R + v_x)^{\frac{3}{2}} - \frac{4}{3} \gamma (V_R + v_y)^{\frac{3}{2}} \right].$$

(2.56)

By neglecting nonlinear terms of the i current Equation (2.57) is obtained as;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left[ (V_C' - V_{FB} - \phi_B) 2 (v_x - v_y) \right]. \tag{2.57}$$

Thus, resistance value can be written as;

$$R = \frac{2(v_x - v_y)}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_C' - V_T)}.$$

(2.58)

The schemes, which are given in Figure 2.7 and Figure 2.8, do not eliminate even nonlinearities completely. It is easy to verify that the scheme in Figure 2.8 will work even if the control voltage components on each gate are different. In particular, if the control component of the bottom transistor's gate is set to zero, and if  $v_y = 0$ , one obtains the circuit of Figure 2.9. Due to the body effect coefficient is zero, the odd nonlinearities are eliminated completely.

#### 2.2.6 Sixth Technique for Nonlinearity Cancellation

In Figure 2.8 if the control voltage of the bottom transistor's gate is set to zero, and if  $v_y$ =0, the circuit, which is shown in Figure 2.9, is obtained. To keep the bottom transistor on, the circuit necessitates the usage of "depletion mode" devices  $(V_T < 0)$ . This scheme does not eliminate even nonlinearities completely. The transistors can purposely be mismatched to increase the quality of linearity, by an amount dependent on fabrication process parameters. The scheme has limited resistance variability compared to the other schemes, because one of the transistors are not controlled by  $V_C$  and represents a practically fixed resistance in parallel with the other transistor. In practical situations with a limited range for  $V_C$ , this may take it difficult to compensate for all fabrication tolerances and environmental changes. The expression for the resistance R for this circuit is different from before, in that  $V_T$  should be replaced by  $2V_T$ .

Figure 2.9 The sixth nonlinearity cancellation technique

The current of the transistors is;

$$i_1 + i_2 = [i_{L1} + i_{L2}] - [i_{N1} + i_{N2}].$$

(2.59)

Nonlinear terms are;

$$i_{N1} = i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2}V_x^2 + \frac{2}{3}\gamma (V_R + v_x)^{3/2} - \frac{2}{3}\gamma (V_R)^{3/2} - W_R^{1/2}v_x\right]. \quad (2.60)$$

Linear terms are;

$$i_{L_1} = i_{L_2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[ \left(V_C + v_x - 2V_T\right) \left(v_x\right) \right]. \tag{2.61}$$

Substituting linear and nonlinear terms into account the transistor current i is obtained as;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left\{ (V_C - 2V_T)(v_x) - \left[\frac{4}{3} \gamma (V_R + v_x)^{\frac{3}{2}} - \frac{4}{3} \gamma (V_R)^{\frac{3}{2}} + 2 \gamma V_R^{\frac{1}{2}}(v_x)\right] \right\}. (2.62)$$

By neglecting nonlinear terms;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left[ \left(V_C - 2V_T\right) \left(v_x\right) \right]. \tag{2.63}$$

These schemes do not eliminate even nonlinearities completely. The resistance value is defined as;

$$R = \frac{v_x}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_C - 2V_T)}.$$

(2.64)

The remaining odd nonlinearities are eliminated completely because body effect coefficient is zero.

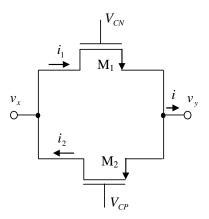

#### 2.2.7 Seventh Technique for Nonlinearity Cancellation

In the seventh nonlinearity cancellation technique, an NMOS and a PMOS transistor is connected parallel as shown in Figure 2.10. Each type of transistor has its own control voltages.

Figure 2.10 The seventh nonlinearity cancellation technique

The current of the transistors is;

$$i_1 - i_2 = [i_{L1} - i_{L2}] - [i_{N1} - i_{N2}].$$

(2.65)

Nonlinear terms are;

$$i_{N1} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_x^2 - v_y^2\right) + \frac{2}{3} \gamma \left(V_R + v_x\right)^{\frac{3}{2}} - \frac{2}{3} \gamma \left(V_R + v_y\right)^{\frac{3}{2}} - \gamma V_R^{\frac{1}{2}} \left(v_x - v_y\right)\right].$$

(2.66)

$$i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{1}{2} \left(v_{y}^{2} - v_{x}^{2}\right) + \frac{2}{3} \gamma \left(V_{R} + v_{y}\right)^{3/2} - \frac{2}{3} \gamma \left(V_{R} + v_{x}\right)^{3/2} - \mathcal{W}_{R}^{1/2} \left(v_{y} - v_{x}\right)\right].$$

(2.67)

$$i_{N} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{4}{3} \gamma (V_{R} + V_{x})^{\frac{3}{2}} - \frac{4}{3} \gamma (V_{R} + V_{y})^{\frac{3}{2}}\right]. \tag{2.68}$$

Linear terms are;

$$i_{L1} = \left(\frac{W}{L}\right) \mu C_{ox} (V_{CN} - V_T) (v_x - v_y).$$

(2.69)

$$i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{CP} - (-V_T)\right) \left(v_y - v_x\right). \tag{2.70}$$

$$i_L = \left(\frac{W}{L}\right) \mu C_{ox} (V_{CN} - V_{CP}) (v_x - v_y).$$

(2.71)

Substituting linear and nonlinear terms into account, the transistor current i is obtained as;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left\{ (V_{CN} - V_{CP})(v_x - v_y) - \left[\frac{4}{3} \gamma (V_R + v_x)^{\frac{3}{2}} - \frac{4}{3} \gamma (V_R + v_y)^{\frac{3}{2}}\right] \right\}. (2.72)$$

By neglecting nonlinear terms;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left[ (V_{CN} - V_{CP}) (v_x - v_y) \right]. \tag{2.73}$$

$$\left(\frac{1}{R_N} + \frac{1}{R_P}\right) = \frac{i}{(v_x - v_y)} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_{CN} - V_{CP})}.$$

(2.74)

This circuit has been used as a crude linear resistor for several years in CMOS opamps and other analog circuits. If the n and p channel devices are purposely mismatched (based on a knowledge of fabrication process parameters), their nonlinearities can be approximately cancel out. Since n and p channel devices are made differently, one cannot expect this scheme to provide high linearity. For zero body effect coefficient, the odd nonlinearities are eliminated completely.

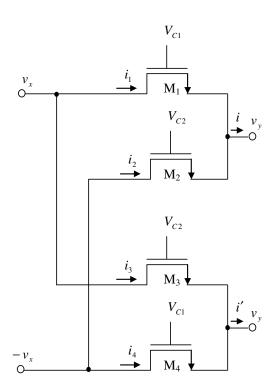

#### 2.2.8 Eighth Technique for Nonlinearity Cancellation

Another technique for nonlinearity cancellation, which is shown in Figure 2.11, consists of four NMOS transistors. The transistors have different control voltages, which are named  $Vc_1$  and  $Vc_2$ , as seen in Figure 2.11.

Figure 2.11 The eighth nonlinearity cancellation technique

The current of the transistors is;

$$i - i' = [(i_{I1} + i_{I2}) - (i_{I3} + i_{I4})] - [(i_{N1} + i_{N2}) - (i_{N3} + i_{N4})]. \tag{2.75}$$

Nonlinear terms are;

$$i_{N_1} = i_{N_3} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{1}{2} \left(v_x^2 - v_y^2\right) + \frac{2}{3} \gamma (V_R + v_x)^{\frac{3}{2}} \\ -\frac{2}{3} \gamma \left(V_R + v_y^2\right)^{\frac{3}{2}} - \mathcal{W}_R^{\frac{1}{2}} \left(v_x - v_y^2\right) \end{bmatrix}.$$

(2.76)

$$i_{N2} = i_{N4} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{1}{2} \left( (-v_x)^2 - v_y^2 \right) + \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} \\ -\frac{2}{3} \gamma (V_R + v_y)^{\frac{3}{2}} - \mathcal{W}_R^{\frac{1}{2}} \left( (-v_x) - v_y \right) \end{bmatrix}.$$

(2.77)

Linear terms are;

$$i_{L_1} = \left(\frac{W}{L}\right) \mu C_{ox} (V_{C_1} - V_T) (v_x - v_y). \tag{2.78}$$

$$i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} (V_{C2} - V_T) (-v_x - v_y). \tag{2.79}$$

$$i_{L_3} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{C2} - V_T\right) \left(v_x - v_y\right).$$

(2.80)

$$i_{L4} = \left(\frac{W}{L}\right) \mu C_{ox} (V_{C1} - V_T) (-v_x - v_y).$$

(2.81)

Taking linear and nonlinear terms into account and neglecting nonlinear terms, the transistor current i - i' is obtained as the following form;

$$i - i' = \left(\frac{W}{L}\right) \mu C_{ox} \left[2(V_{C1} - V_{C2})(v_x)\right]. \tag{2.82}$$

$$\left(\frac{1}{R_1} + \frac{1}{R_2}\right) = \frac{2v_x}{i - i'} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_{C1} - V_{C2})}.$$

(2.83)

The circuit in Figure 2.11 achieves in principle complete cancellation of both even and odd nonlinearities. In this figure,  $R_1$  and  $R_2$  are the resistance values.

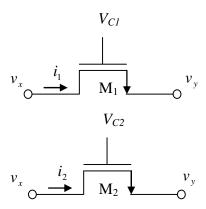

#### 2.2.9 Ninth Technique for Nonlinearity Cancellation

This technique is similar to the third nonlinearity cancellation technique. Only difference is both NMOS's source and drain are connected to the same voltage as depicted in Figure 2.12. Each transistor has its own control voltage.

Figure 2.12 The ninth nonlinearity cancellation technique

Nonlinear and linear terms can be defined as the following form;

$$i_{N1} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{1}{2} \left(v_x^2 - v_y^2\right) + \frac{2}{3} \gamma (V_R + v_x)^{\frac{3}{2}} \\ -\frac{2}{3} \gamma \left(V_R + v_y^2\right)^{\frac{3}{2}} - \mathcal{W}_R^{\frac{1}{2}} \left(v_x - v_y^2\right) \end{bmatrix}.$$

(2.84)

$$i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \begin{bmatrix} \frac{1}{2} \left( (v_x)^2 - (v_y)^2 \right) + \frac{2}{3} \gamma (V_R + v_x)^{\frac{3}{2}} \\ -\frac{2}{3} \gamma (V_R + v_y)^{\frac{3}{2}} - W_R^{\frac{1}{2}} \left( v_x - v_y \right) \end{bmatrix}.$$

(2.85)

$$i_{L1} = \left(\frac{W}{L}\right) \mu C_{ox} (V_{C1} - V_T) (v_x - v_y). \tag{2.86}$$

$$i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{C2} - V_T\right) \left(\left(v_x\right) - \left(v_y\right)\right). \tag{2.87}$$

Nonlinear term of the current  $i_{N1} - i_{N2}$  can be calculated as the following form;

$$i_{N1} - i_{N2} = \left(\frac{W}{L}\right) \mu C_{ox} \left[\frac{2}{3} \gamma (V_R + v_x)^{\frac{3}{2}} - \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} - 2 \gamma W_R^{\frac{1}{2}} (v_x) - \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} + \frac{2}{3} \gamma (V_R - v_x)^{\frac{3}{2}} + 2 \gamma W_R^{\frac{1}{2}} (v_x)\right]. \quad (2.88)$$

Linear term of the current  $i_{L1} - i_{L2}$  can be written as the following form;

$$i_{L1} - i_{L2} = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{C1} - V_{C2}\right) \left(v_x - v_y\right). \tag{2.89}$$

The transistor current  $i_1 - i_2$ , which is defined as  $[i_{L1} - i_{L2}] - [i_{N1} - i_{N2}]$ , can be written as;

$$i_1 - i_2 = \left(\frac{W}{L}\right) \mu C_{ox} \left[ (V_{C1} - V_{C2}) v_x - v_y) \right]. \tag{2.90}$$

Thus, the resistance value can be calculated as;

$$i = \left(\frac{W}{L}\right) \mu C_{ox} \left(V_{C1} - V_{C2}\right) (v_x - v_y). \tag{2.91}$$

$$R = \frac{(v_x - v_y)}{i} = \frac{1}{\left(\frac{W}{L}\right)\mu C_{ox}(V_{C1} - V_{C2})}.$$

(2.92)

By using this scheme, both the even and the odd nonlinearities are eliminated (Ismail & Fiez, 1994; Salama & Soliman, 1999a).

#### 2.2.10 Tenth Nonlinearity Cancellation Technique

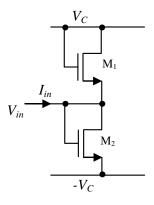

This technique uses two NMOS transistors, which are operating in saturation region, as shown in Figure 2.13.

Figure 2.13 The tenth nonlinearity cancellation technique

The matched two transistors  $M_1$  and  $M_2$  are diode connected. Using square law characteristic, the drain currents in  $M_1$  and  $M_2$  can be expressed as;

$$Id_{1} = \frac{\mu_{n} C_{ox}}{2} \frac{W}{L} (V_{C} - V_{in} - V_{T})^{2}, \qquad (2.93)$$

$$Id_{2} = \frac{\mu_{n}C_{ox}}{2} \frac{W}{L} (V_{in} - (-V_{C}) - V_{T})^{2}.$$

(2.94)

A voltage  $V_{in}$  is applied to the central node of the electronic resistor circuit, developing a current  $I_{in}$  into the node. Using Kirchhoff's current law with Equations (2.93) and (2.94), a simple algebraic expression can be obtained for the resistance as;

$$R = \frac{V_{in}}{I_{in}} = \frac{L}{2\mu_n C_{ox} W(V_C - V_T)},$$

(2.95)

Equation (2.95) is true when both NMOS transistors remain in saturation region, which is true if  $|V_{in}| \langle (V_C - V_T)$ . The MOSFET resistor is useful for cases with high desired linearity but reduced circuit complexity. The price paid for this is however two control voltage sources  $(V_C)$  instead of one (Wang, 1990; Metin, Pal & Cicekoglu, 2010).

#### 2.3 Comparison of The Nonlinearity Cancellation Techniques

For proper cancellation of even order distortion in the presented schemes, one would need perfect transistor matching. In practice, mismatches will induce some residual even order distortion. The dominant source for such mismatches appears to be threshold voltage mismatch. Although, in the filters  $V_C - V_T$  can be large, thus reducing this effect and allowing matching as well as 0.1 to 0.5 percent for adjacent MOSFET resistors. Another nonideality is that the mobility  $\mu$  is not really constant, but changes slightly with the terminal voltages. However, even order distortion is not really affected by this, odd order distortion can be somewhat different than expected by supposing  $\mu$  is constant. Actually, the behavior of the circuits in Figure 2.4, Figure 2.5, Figure 2.6, Figure 2.11 and Figure 2.12 may be rather similar, especially if their distortion is dominated by even order terms due to mismatches. Connecting substrate to source, the odd nonlinearities are fully cancelled. Table 2 shows the cancellation features of the nonlinearity cancellation techniques which are mentioned above. The performance of these circuits and cancellation techniques 1, 2, 3, 8, 9 and 10 are so good due to the terminal voltages of the transistors. Figure 2.13 is suitable for high frequency operations due to operating in saturation region, but it requires two control voltages.

Table 2.1 Companision of Nonlineanty Cancellation Techniques for y=0

| Figure 2.13                                                                                            | 2                        | Fully                               | Fully                                |

|--------------------------------------------------------------------------------------------------------|--------------------------|-------------------------------------|--------------------------------------|

| Figure 2.4 Figure 2.5 Figure 2.7 Figure 2.8 Figure 2.9 Figure 2.10 Figure 2.11 Figure 2.12 Figure 2.13 | 2                        | Fully                               | Fully                                |

| Figure 2.11                                                                                            | 4                        | Fully                               | Fully                                |

| Figure 2.10                                                                                            | 2                        | Fully                               | Not Fully                            |

| Figure 2.9                                                                                             | 2                        | Fully                               | Not Fully                            |

| Figure 2.8                                                                                             | 2                        | Fully                               | Not Fully Not Fully Not Fully        |

| Figure 2.7                                                                                             | 1                        | Fully                               | Not Fully                            |

| Figure 2.6                                                                                             | 2                        | Fully                               | Fully                                |

| Figure 2.5                                                                                             | 2                        | Fully                               | Fully                                |

| Figure 2.4                                                                                             | 1                        | Fully                               | Fully                                |

|                                                                                                        | Number of<br>Transistors | Cancelling<br>Odd<br>Nonlinearities | Cancelling<br>Even<br>Nonlinearities |

#### **CHAPTER THREE**

# SUITABLE ACTIVE COMPONENTS FOR NONLINEARITY CANCELLATION TECHNIQUES

In this Chapter, suitable active components namely op-amp, operational transresistance amplifier, first generation current conveyor, second generation current conveyor, third generation current conveyor, inverting second generation curret conveyor, differential voltage current conveyor, differential difference current conveyor in IC technology for nonlinearity cancellation techniques are presented. The historical background, block diagram and terminal port relations of the components are given.

#### 3.1 Operational Amplifiers

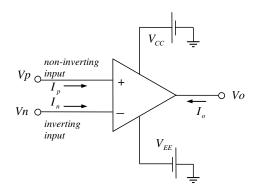

An op-amp is a high gain electronic voltage amplifier with differential inputs and, usually, a single output. The symbol of the op-amp with the associated terminals is shown in Figure 3.1.

Figure 3.1 Symbol notation of op-amp

The power supply voltages  $V_{CC}$  and  $V_{EE}$  power the op-amp and generally define the output voltage range of the amplifier. The terminals, which are tagged with the "+" and the "-" signs, are called non-inverting and inverting inputs, respectively. The input voltage  $V_p$  and  $V_n$  and the output voltage  $V_o$  are referenced to ground.

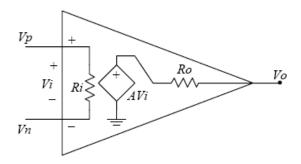

The equivalent circuit model of an op-amp is shown in Figure 3.2.

Figure 3.2 Equivalent circuit model of op-amp

The voltage  $V_i$  is the differential input voltage  $V_i = V_p - V_n$ .  $R_i$  is the input resistance of the device and  $R_o$  is the output resistance. The gain parameter A is called the open loop gain.

The output voltage is;

$$Vo = AVi = A(Vp - Vn). (3.1)$$

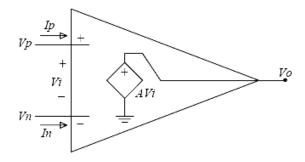

The ideal op-amp model is shown schematically in Figure 3.3.

Figure 3.3 Ideal op-amp model

The ideal op-amp conditions in the negative feedback are;

$$Vp = Vn$$

$Ip = In = 0$

$Ri \rightarrow \infty$  (3.2)

$Ro = 0$

$A \rightarrow \infty$

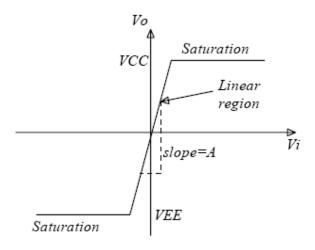

The voltage transfer curve of the op-amp, which relates the output voltage to the input voltage, is shown in Figure 3.4.

Figure 3.4 Op-amp voltage transfer characteristics

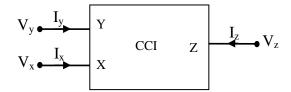

#### **3.2 Current Conveyors**

As an alternative active element to classical voltage mode op-amps current conveyor received great attention in recent years. The classical op-amp with its high input impedance and low output impedance is a suitable element for voltage mode circuits. However, the current conveyor (CC) has one high (ideally infinite) and one low (ideally zero) input impedance and one high output impedance. These properties make the current conveyor a suitable element for both voltage mode and current mode applications. The first current conveyor, named a first generation current conveyor (CCI) is a 3-port device, which was introduced by Smith and Sedra in 1968 (Smith & Sedra, 1968). Its block diagram representation is shown in Figure 3.5.

Figure 3.5 Circuit symbol of the CCI

In mathematical terms, CCI is described by the following matrix equation;

$$\begin{bmatrix} V_x \\ I_y \\ I_z \end{bmatrix} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}.$$

(3.3)

Taking the non-idealities of the CCI into account, the above hybrid equation can be rewritten as;

$$\begin{bmatrix} V_x \\ I_y \\ I_z \end{bmatrix} = \begin{bmatrix} \beta & 0 & 0 \\ 0 & 1 & 0 \\ 0 & \pm \alpha & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}. \tag{3.4}$$

In Equation (3.4),  $\beta=1-\varepsilon_{\nu}$  is the voltage gain, and  $\alpha=1-\varepsilon_{i}$  is the current gain of the CCI, where  $\varepsilon_{\nu}$  denotes the voltage tracking error between the X and Y terminals and  $\varepsilon_{i}$  denotes the current tracking error between the Z and X terminals. In Equation (3.3), the positive sign indicates the positive-type first generation current conveyor (CCI+) and the negative sign indicates the negative-type first generation current conveyor (CCI-).

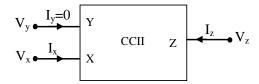

CCI had distortion and accuracy limitations due to base current errors and output impedance restrictions (Wandsworth, 1990). Therefore, Sedra and Smith, (1970) introduced a more versatile building block named as the second generation current conveyor (CCII) that have different features over CCI. The block diagram representation of CCII is shown in Figure 3.6.

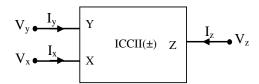

Figure 3.6 Circuit symbol of the CCII

The operation of the CCII can be characterized by the following equations;

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ 1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}. \tag{3.5}$$

Taking the non-idealities of the CCII into account, the above terminal equations can be rewritten as;

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ \beta & 0 & 0 \\ 0 & \pm \alpha & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}. \tag{3.6}$$

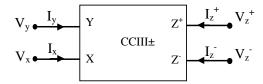

The third generation current conveyor (CCIII) was introduced by Alain Fabre, (1995). The main difference between CCI, CCII and CCIII is relation between terminal Y and terminal X current. In CCI, Y current is equal to X current in the same direction and in the CCII, there is no current flows in terminal Y. But in the CCIII, terminal Y current is equal to X terminal current in the opposite direction (Fabre, 1995). The block diagram representation of CCIII is shown in Figure 3.7 where the positive and negative signs define a positive and negative current conveyor, respectively.

Figure 3.7 Circuit symbol of the CCIII

The operation of the CCIII can be characterized by the following equations;

$$\begin{bmatrix} I_{y} \\ V_{x} \\ I_{z+} \\ I_{z-} \end{bmatrix} = \begin{bmatrix} 0 & -1 & 0 & 0 \\ 1 & 0 & 0 & 0 \\ 0 & 1 & 0 & 0 \\ 0 & -1 & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{y} \\ I_{x} \\ V_{z+} \\ V_{z-} \end{bmatrix}.$$

(3.7)

Taking the non-idealities of the CCIII into account, the above terminal equations can be rewritten as;

$$\begin{bmatrix} I_{y} \\ V_{x} \\ I_{z+} \\ I_{z-} \end{bmatrix} = \begin{bmatrix} 0 & -1 & 0 & 0 \\ \beta & 0 & 0 & 0 \\ 0 & \alpha & 0 & 0 \\ 0 & -\alpha & 0 & 0 \end{bmatrix} \begin{bmatrix} V_{y} \\ I_{x} \\ V_{z+} \\ V_{z-} \end{bmatrix}.$$

(3.8)

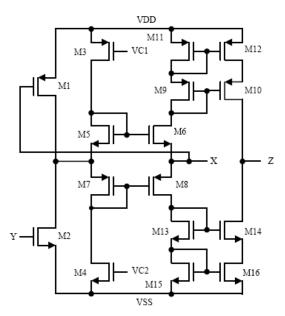

In 1999, the inverting type current conveyor is introduced by Awad and Soliman, (1999), that exhibits an inverting property between the input terminal voltages. The circuit symbol of the second generation inverting current conveyor (ICCII) is shown in Figure 3.8,

Figure 3.8 Circuit symbol of the ICCII

where the positive sign indicates the positive type inverting second generation current conveyor (ICCII+) and the negative sign indicates the negative type inverting second generation current conveyor (ICCII-).

The operation of the ICCII can be characterized by the following equations;

$$\begin{bmatrix} I_y \\ V_x \\ I_z \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ -1 & 0 & 0 \\ 0 & \pm 1 & 0 \end{bmatrix} \begin{bmatrix} V_y \\ I_x \\ V_z \end{bmatrix}. \tag{3.9}$$

In non-ideal case, ICCII is characterized by the following port relations;

$$\begin{bmatrix} I_{y} \\ V_{x} \\ I_{z} \end{bmatrix} = \begin{bmatrix} 0 & 0 & 0 \\ -\beta & 0 & 0 \\ 0 & \pm \alpha & 0 \end{bmatrix} \begin{bmatrix} V_{y} \\ I_{x} \\ V_{z} \end{bmatrix}.$$

(3.10)

#### 3.3 Differential Voltage Current Conveyor

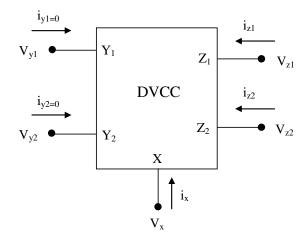

H. O. Elwan and A. M. Soliman proposed Differential Voltage Current Conveyor (DVCC), which is an extension of the CCII in 1997. CCII allowed opportunities to the designers as a versatile building block to implement many high performance circuits. On the other hand, CCII has only one input terminal with infinite impedance, so it does not allow the designers to perform circuits, which are supposed to handle differential inputs by using a single CCII (Elwan & Soliman, 1997). Moreover, one of the most productive dual CCII based amplifier circuits proposed in the literature, which is supposed to handle differential input signals despite its high common mode rejection ratio brings a disadvantage because of the non-zero input impedance of X terminal of CCII (Elwan & Soliman, 1997). For overcoming these disadvantages of having unique high impedance input terminal, DVCC was proposed.

DVCC is a five ports device, which is a versatile building block specifically designed for floating inputs, as depicted in Figure 3.9. So, it is formed up to have two distinct infinite impedance input terminals  $(Y_1 \text{ and } Y_2)$ , which allows no current flowing through Y terminals. DVCC has fundamentally designed for differential inputs. Therefore the potential difference between terminals  $Y_1$  and  $Y_2$  is equal to X terminal potential (Incekaraoglu, 2007).

Figure 3.9 Circuit symbol of DVCC

The current, which flows through terminal X, is conveyed to the dual Z terminal. One of them is the same and the other one is inverse polarity, as shown in matrix Equation (3.11).

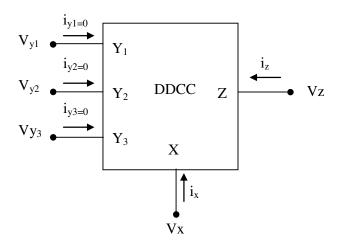

#### 3.4 Differential Difference Current Conveyor

Differential Difference Current Conveyor (DDCC) is introduced in 1996 by Chiu, Liu, Tsao and Chen. DDCC is a five port device as given in Figure 3.10. DDCC is designed to have three distinct infinite impedance input terminals (Y<sub>1</sub>,Y<sub>2</sub> and Y<sub>3</sub>) which allows no current flowing through Y terminals. X terminal has the equal potential to the potential difference between terminals Y<sub>1</sub> and Y<sub>2</sub> plus the potential of Y<sub>3</sub> (Chiu, Liu, Tsao & Chen, 1996). Relying on the common current conveying characteristic, current flowing through terminal X is conveyed to the Z terminal. DDCC is named as either DDCC+ or DDCC- depending on the polarity of the current flowing through Z terminal. In DDCC+, the current flowing through terminal

Z has the same polarity with the current flowing through X terminal, whereas in DDCC-, the current is conveyed from X terminal to Z terminal with an inverse polarity (Incekaraoglu, 2007).

Figure 3.10 Circuit symbol of DDCC

The matrix representation of DDCC is given in Equation (3.12) (Chiu, Liu, Tsao & Chen, 1996).

All of the above mentioned conveyors and the derived conveyor types have been used in construction of many complex circuits and systems so far. Today, current conveyor can be considered as one of the most famous building blocks for analog integrated circuit and system design.

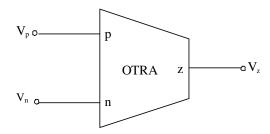

#### 3.5 Operational Transresistance Amplifier

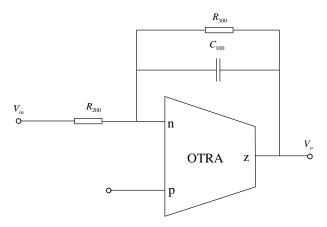

OTRA is a high gain current input, voltage output device. The circuit symbol of the OTRA is illustrated in Figure 3.11.

Figure 3.11 Circuit symbol of the OTRA

The operation of the OTRA can be characterized by the following equations;

$$V_z = R_m (I_p - I_n)$$

$$V_p = V_n = 0$$

(3.13)

The OTRA, which is known also as current differencing amplifier or Norton amplifier, is an important active element in analog ICs and systems. Both input and output terminals of OTRA are characterized by low impedance, thereby eliminating response limitations incurred by capacitive time constants. Since the input terminals of OTRA are at ground potential, most effects of parasitic capacitances and resistances disappear. The output terminal of OTRA exhibits low impedance so that OTRA based voltage mode circuits can easily be cascaded without additional buffers. For ideal operation, the transresistance  $R_m$  approaches infinity forcing the input currents to be equal. Thus, the OTRA must be used in a feedback configuration in a way that is similar to the classical op-amp (Salama & Soliman, 1999a; Kılınç, 2006).

OTRA has the advantages of high slew rate and wide bandwidth due to the fact that it benefits from the current processing capabilities at the input terminals. On the other hand, since its output terminal is characterized as low impedance, OTRA is suitable for voltage mode operations keeping the compatibility with existing signal processing circuits (Salama & Soliman, 1999a).

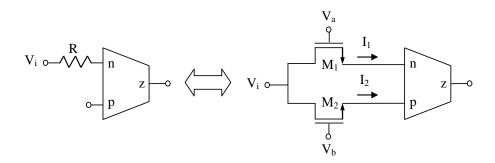

The first and second nonlinearity cancellation techniques can be used with ICCII, DDCC and DVCC. The opposite but same terminal voltage values can achieve by grounding the required ports of the DDCC and DVCC.

The third nonlinearity cancellation technique can be used with OP-AMP, OTRA, DDCC and DVCC. The source voltages of the NMOS transistors can be connect to the input terminals of the active elements which are mentioned above.

The fourth, fifth, sixth, seventh and tenth nonlinearity cancellation techniques can be used with CCs, OP-AMP and OTRA. These techniques need signal dependent control voltages.

The eighth and ninth nonlinearity cancellation techniques can be used with OP-AMP, OTRA, DDCC and DVCC.

The nonlinearity cancellation techniques which are used for grounded resistors can be used all active elements.

#### **CHAPTER FOUR**

## COMPARING NONLINEARITY CANCELLATION TECHNIQUES WITH INTEGRATOR

In this chapter, performance comparison of mostly used four nonlinearity cancellation techniques, which are previously mentioned in Chapter 2, is presented. An integrator circuit was used for the comparison. All active components and capacitors used for integrator expect resistors are ideal. The resistors are implemented via MOS transistors. Thus, only MOS transistors affect the linearity of the integrator circuit. Transient, THD and frequency analyses of the MOS transistors are compared. In all of the comparisons for integrators, the same input signal ( $V_{in}$ ) of amplitude 10mV and 1.2 MHz frequency are used. PSPICE simulation program and 0.35 $\mu$ m TSMC MOSIS process model parameters are used for the analyses.

#### 4.1 Op-Amp Based Integrators

#### 4.1.1 Miller Integrator

The Miller integrator circuit active and passive components of which are ideal is shown in Figure 4.1. Applying input signal to integrator the output waveform is obtained as depicted in Figure 4.2.

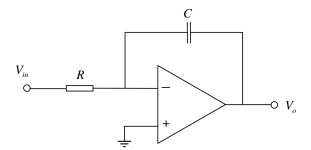

Figure 4.1 Miller integrator with ideal R

For an ideal integrator amplifier, the output voltage is written as;

$$V_{out} = -\frac{1}{RC} \int V_{in} dt . (4.1)$$

Figure 4.2 Output waveform of Miller integrator with ideal R

Figure 4.3 Frequency analysis of Miller integrator with ideal R

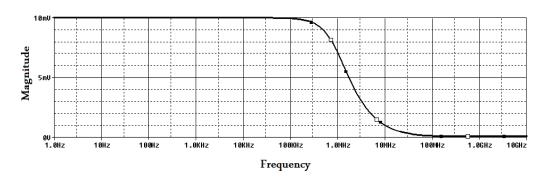

Figure 4.3 shows the frequency analysis of the Miller integrator amplifier with the output gain equal to 1. The resistor in Figure 4.1 can be implemented by two NMOS transistors which are previously expressed in Section 2.2.6. Using the sixth implementation technique, the resistance value can be controlled via changing  $V_C$  voltage. So integrator parameters can be controlled electronically. Figure 4.4 shows the MOS-C realization of the Miller integrator with the sixth nonlinearity cancellation technique.

Figure 4.4 MOS-C realization of Miller integrator (Babanezhad & Temes, 1984)

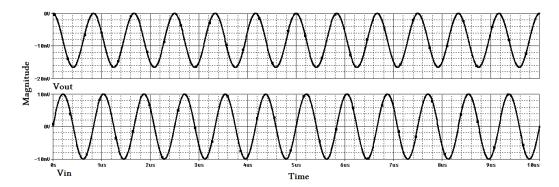

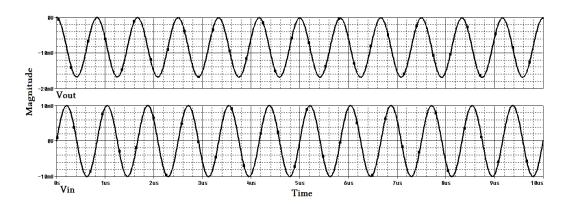

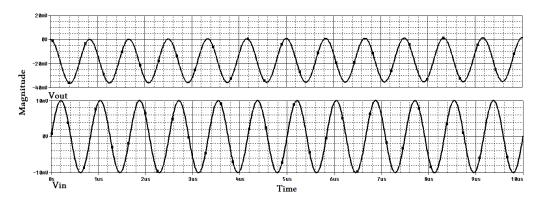

Simulating MOS-C Miller integrator which is shown in Figure 4.4 with the input signal  $V_{in}$  the obtained output waveform is shown in Figure 4.5.

Figure 4.5 Output waveform of MOS-C Miller integrator

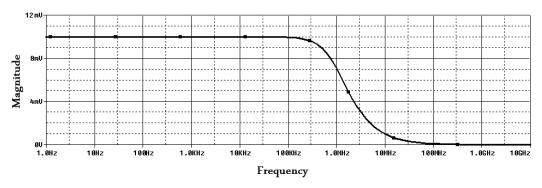

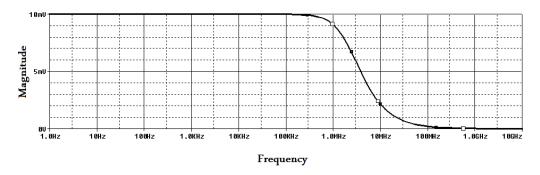

With the output gain equal to 1; the frequency analysis of the integrator, which is shown in Figure 4.4, is depicted in Figure 4.6.

Figure 4.6 Frequency analysis of Miller integrator

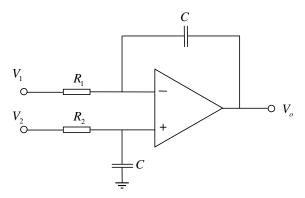

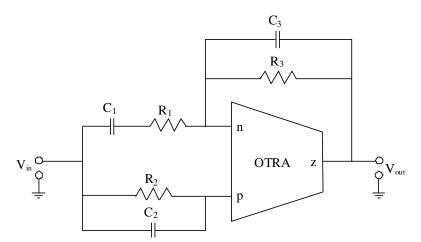

#### 4.1.2 Op-amp Integrator

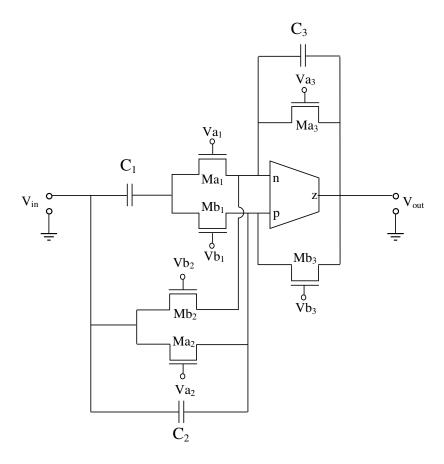

Another op-amp based integrator circuit is shown in Figure 4.7 (Ismail, Smith & Beale, 1988). The circuit consists of two resistors suitable for realization with four NMOS transistors, two capacitors and an op-amp for an active element.

Figure 4.7 Op-amp based integrator circuit

If the resistors  $R_1$  and  $R_2$  are implemented via MOS transistors as mentioned in Section 2.2.8. The resultant MOS-C integrator becomes as depicted in Figure 4.8.

Figure 4.8 MOS-C realization of op-amp integrator circuit

Via changing gate voltages of NMOS transistors the resistance value and so integrator parameters can be changed electronically. Figure 4.9 shows the output waveform of the MOS-C op-amp integrator circuit shown in Figure 4.8. Input signal is given from the  $V_1$  port and the  $V_2$  port has been grounded.

Figure 4.9 Output waveform of the MOS-C op-amp integrator

Figure 4.10 depicts the frequency analysis of the op-amp integrator shown in Figure 4.8 with the output gain equal to 1.

Figure 4.10 Frequency analysis of Op-amp. integrator

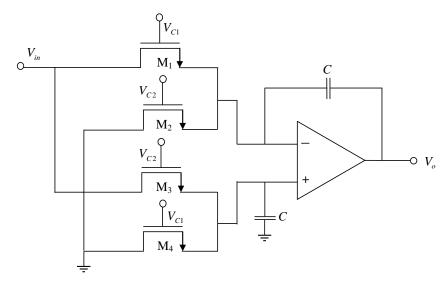

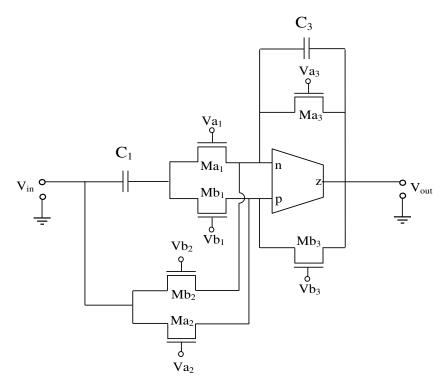

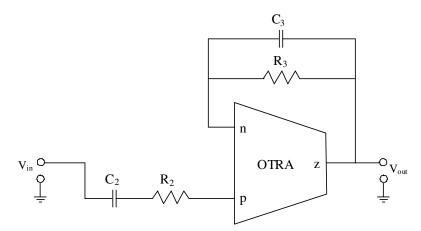

### **4.2 OTRA Based Integrator**

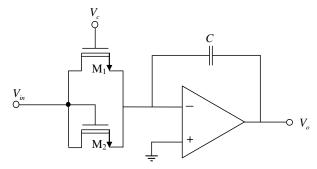

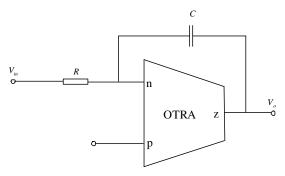

An OTRA based integrator is shown in Figure 4.11.

Figure 4.11 OTRA based integrator

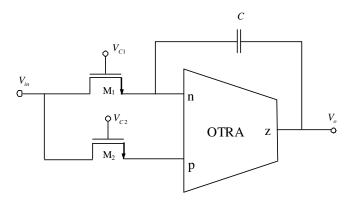

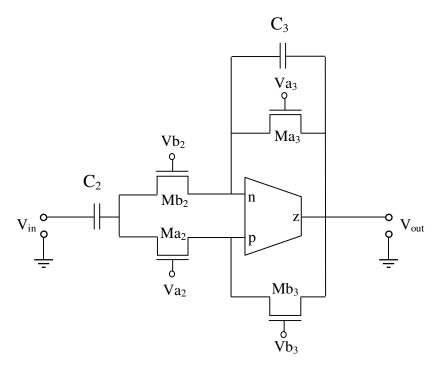

Implementing the resistor with two matched MOS transistors as mentioned previously in Section 2.2.9, the OTRA based integrator becomes as Figure 4.12. Changing the gate voltages of the transistors  $M_1$  and  $M_2$  the tunable resistance value and integrator parameters can be obtained.

Figure 4.12 MOS-C realization of OTRA based integrator

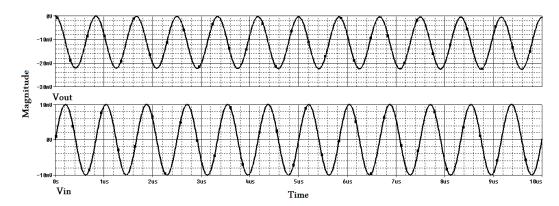

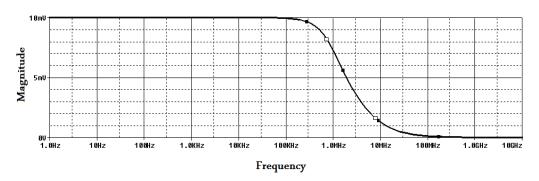

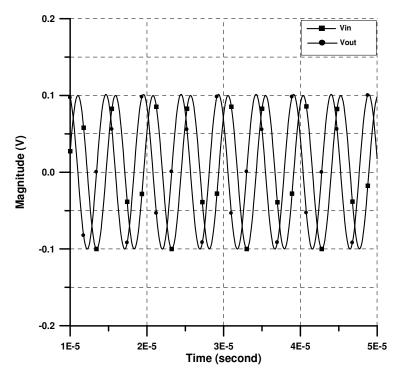

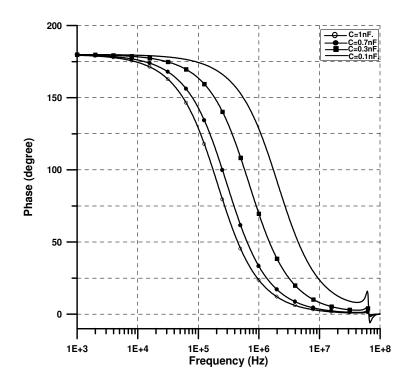

Figure 4.13 depicts the output waveform of the MOS-C realization of OTRA based integrator with the input signal  $V_{in}$ . Figure 4.14 shows the frequency analysis of the OTRA based integrator with the output gain equal to 1.

Figure 4.13 Output waveform of MOS-C integrator in Figure 4.12

Figure 4.14 Frequency analysis of OTRA based integrator

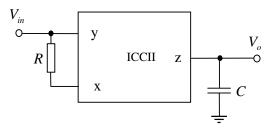

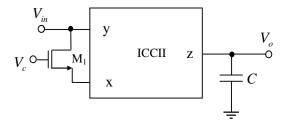

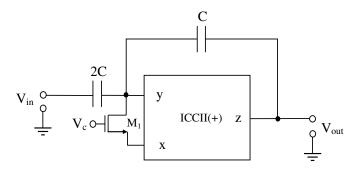

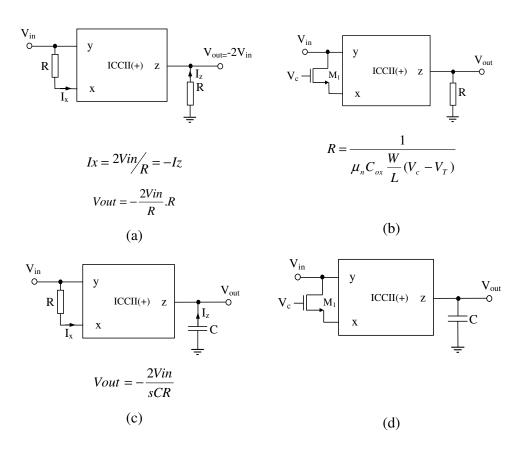

#### 4.3 ICCII Based Integrator

An ICCII based integrator is shown in Figure 4.15 (Toker & Zeki, 2007).

Figure 4.15 ICCII based integrator

Because of the input terminals of ICCII which are the same positive and negative voltages the resistor can be implemented easily using a MOS transistor. The MOS-C realization of the ICCII based integrator is shown in Figure 4.16. Resistor implementation technique was mentioned previously in Section 2.2.1.

Figure 4.16 MOS-C realization of ICCII based integrator

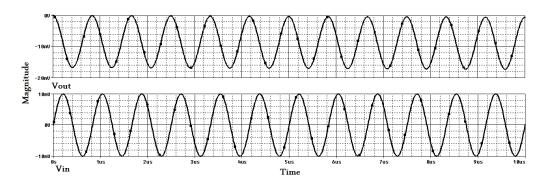

Changing the gate voltage of the NMOS transistor electronically adjustable resistance and integrator parameters can be obtained. The output waveform of the MOS-C realization of ICCII based integrator is shown in Figure 4.17.

Figure 4.17 Output waveform of MOS-C ICCII based integrator

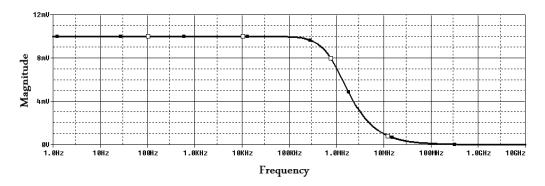

Figure 4.18 Frequency analysis of ICCII based integrator

With the output gain equal to 1; the frequency analysis of the ICCII based integrator is depicted in Figure 4.18.

#### 4.4 Performance Comparison

In this section, performance comparison of the integrator is presented. The THDs of the integrators, which are mentioned above with the MOS-C realization techniques, are shown in Table 4.1. As seen in Table 4.1, Miller integrator has the best THD analysis performance. But the implementation technique, which is used for Miller integrator, is not suitable for higher frequencies.

Table 4.1. THD Analysis of the MOS-C based integrator amplifiers

|                        | THD Analysis |

|------------------------|--------------|

| Miller integrator      | 0.076%       |

| Op-Amp. integrator     | 0.158%       |

| OTRA based integrator  | 0.176%       |

| ICCII based integrator | 0.219%       |

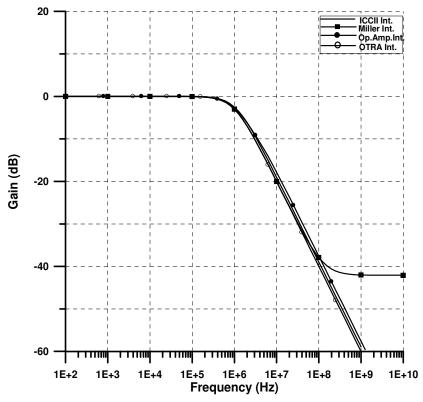

The frequency analysis of the four integrators, which are mentioned above, is shown in Figure 4.19.

Figure 4.19 Frequency analysis of four integrators

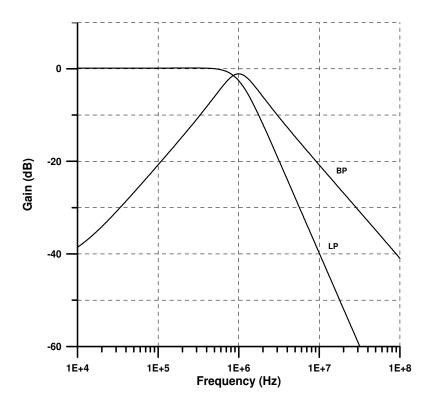

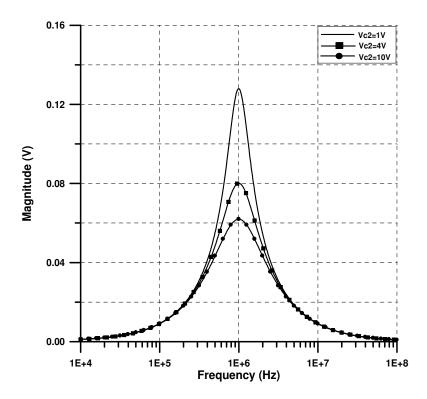

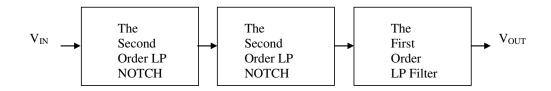

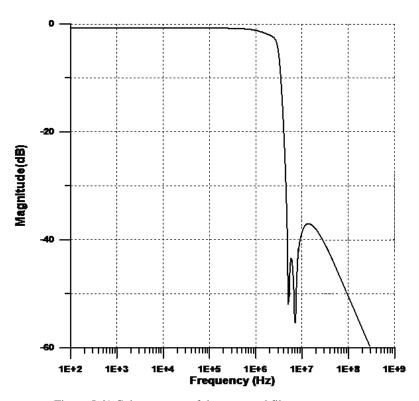

### CHAPTER FIVE PROPOSED MOS-C BASED CIRCUITS

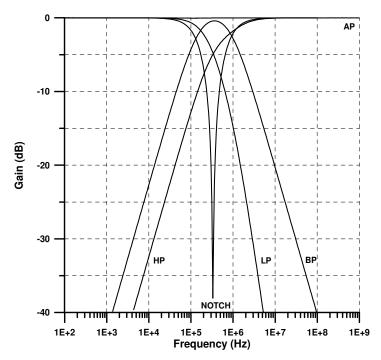

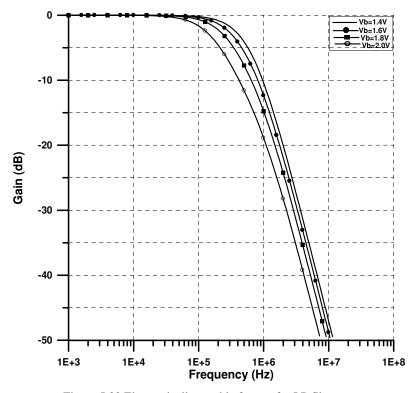

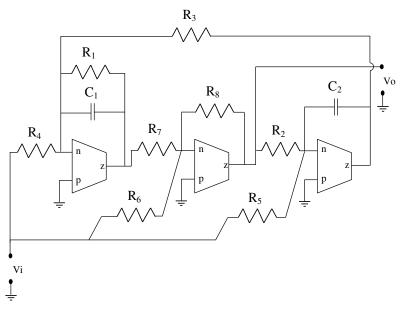

In this Chapter, new filter and oscillator topologies with MOS-C realization approach are presented. Chapter 5 started with two new first order allpass filters which include one active element. Then, three biquadratic filter configurations are presented. The second order lowpass, highpass, bandpass, and notch filters are realized using these biquadratic filter configurations. An electronically variable frequency oscillator configuration is obtained from the previously reported general configuration with a modification is modified. Tow Thomas and quadrature oscillator configurations are also given. The proposed configurations can be made fully integrated based on MOS-C realization. In addition, the proposed filters and oscillators have electronically tunable feature without affecting other critical parameters. The natural frequency and the quality factor are controllable independently. The CMOS equivalents of the active elements consist of MOS transistors. The ideal equivalents of active elements consist of only controlled sources.

#### 5.1 First Order Allpass Filters

Filters are one of the necessary building blocks of many analog signal processing applications. Especially, first order filters are widely used in audio and video, as well as in many applications where the simplicity and power consumption are important parameters. Allpass (AP) filters are generally used for frequency-dependent delays yielding constant output amplitude over a desired frequency range. Other types of active circuits such as oscillators and high Q band pass filters are also realized by using allpass filters (Schauman & Van Valkenburg, 2001; Toker, Ozoguz, Cicekoglu & Acar, 2000).

A large number of first order allpass filter exist in the literature. Allpass filter based on op-amps are proposed in (Soliman, 1973). Op-amp based filters suffer from limited bandwidth performance.

Hereby, several allpass filters using active devices have been reported such as a CCII, (Soliman, 1997; Cicekoglu, Kuntman & Berk, 1999; Khan & Maheshwari, 2000; Horng, Hou, Chang, Chung, Liu & Lin, 2006), ICCII (Ibrahim, Kuntman, Ozcan & Çiçekoglu, 2004) CCIII (Maheshwari & Khan, 2001), DVCC (Minaei & Ibrahim, 2005), DDCC (Horng, Hou, Chang, Lin, Shiu & Chiu, 2006), OTRA (Cakir, Çam & Cicekoglu, 2005). Nevertheless, most of them lack an electronically controllable phase response. Some others have a phase response that is adjusted by a biasing current of the current conveyors (Pandey & Paul, 2004; Minaei & Cicekoglu, 2006; Maheshwari, 2005; Öztayfun, Kılınç, Çelebi, & Çam, 2008; Tangsrirat, Pukkalanun, & Surakampontorn, 2010). However, among the above mentioned studies do not include voltage controlled phase shifter.

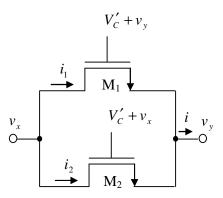

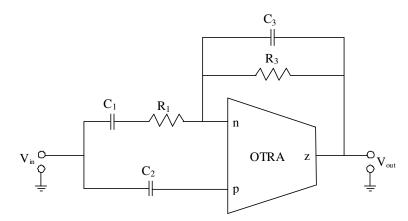

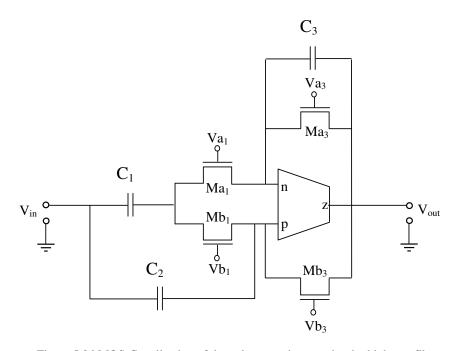

#### 5.1.1 First Topology for First Order Allpass Filter

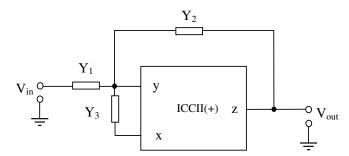

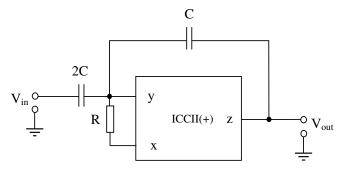

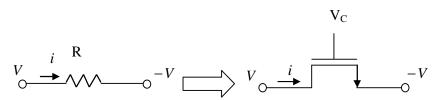

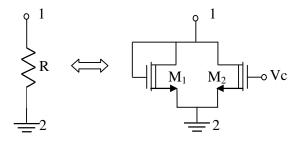

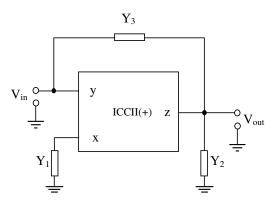

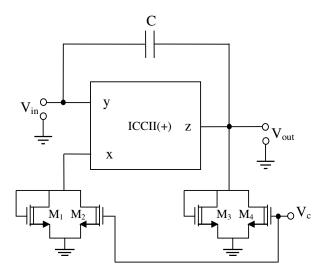

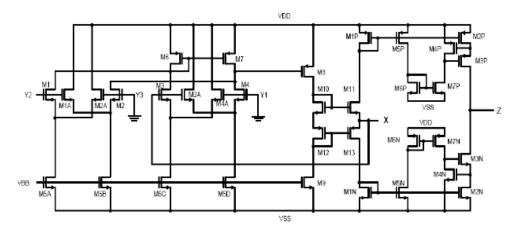

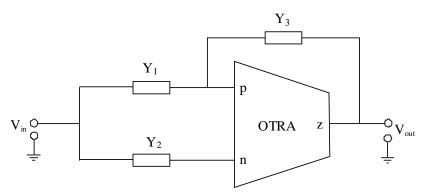

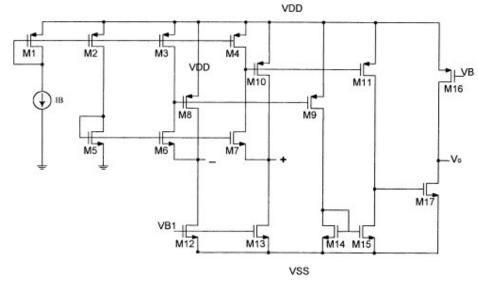

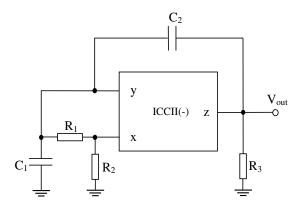

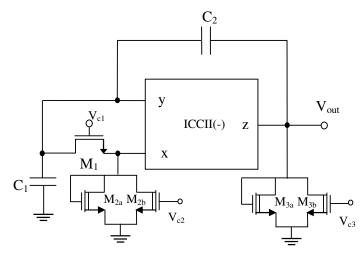

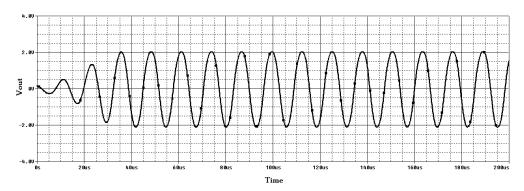

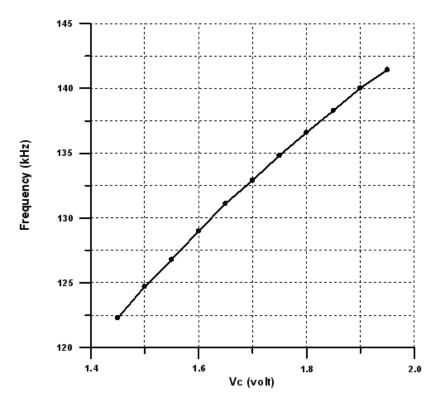

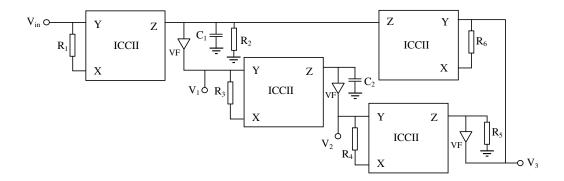

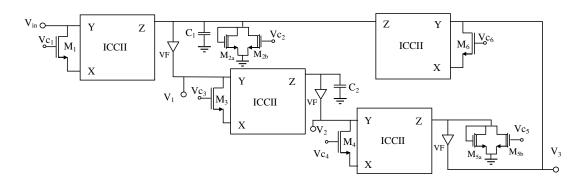

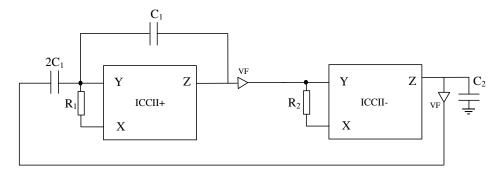

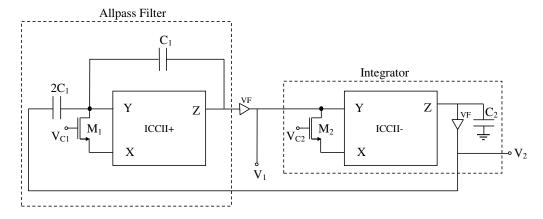

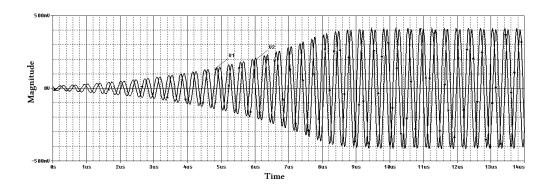

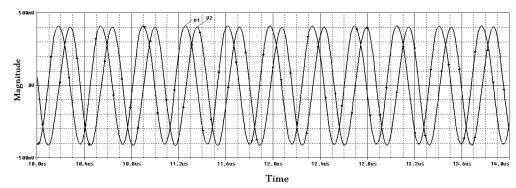

A novel application of ICCII as a voltage controlled electronically tunable allpass filter is proposed. The proposed topology for the first order allpass filter is shown in Figure 5.1.

Figure 5.1 First order allpass filter topology

In ideal case, the transfer function of the proposed topology in Figure 5.1 is found as;

$$\frac{V_{out}}{V_{in}} = \frac{Y_1(Y_2 - 2Y_3)}{Y_2(Y_1 + 4Y_3)}.$$

(5.1)

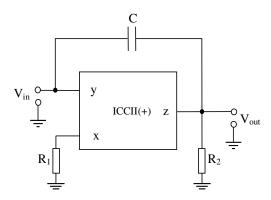

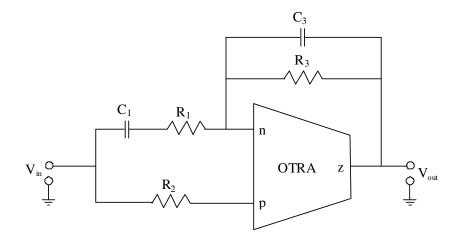

Choosing appropriate admittances in Equation (5.1) as  $Y_1 = s2C$ ,  $Y_2 = sC$ ,  $Y_3 = G$ , allpass filter response can be obtained as shown in Figure 5.2. Hereby, the proposed

allpass circuit employs ICCII(+), two capacitors and a resistor that is suitable for MOS realization.

Figure 5.2 First order allpass filter configuration

Routine analysis yields the transfer function as;

$$\frac{V_{out}}{V_{in}} = \frac{s - \frac{2}{RC}}{s + \frac{2}{RC}}.$$

(5.2)

The natural frequency,  $\omega_o$ , can be found as;

$$\omega_o = \frac{2}{RC}. ag{5.3}$$

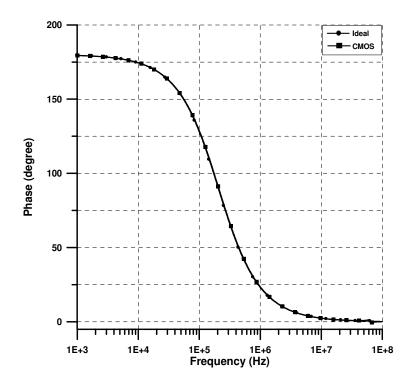

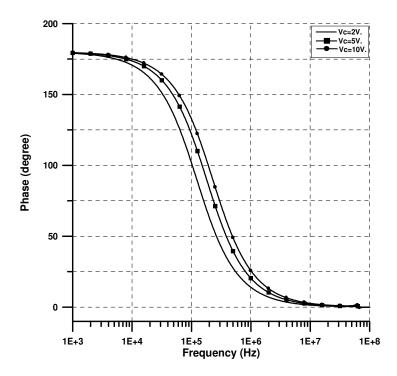

The phase response of the filter can be calculated as;

$$\varphi(\omega) = 180^{\circ} - 2\arctan(\frac{\omega}{\omega_0}). \tag{5.4}$$

In non-ideal case, ICCII is characterized by the following port relations;

$$I_{y} = 0, V_{x} = -\beta . V_{y}, I_{z} = \pm \alpha . Ix$$

(5.5)

In Equation (5.5),  $\beta=1-\varepsilon_{\nu}$  is the voltage gain, and  $\alpha=1-\varepsilon_{i}$  is the current gain of the ICCII, where  $\varepsilon_{\nu}$  denotes the voltage tracking error between the X and Y terminals and  $\varepsilon_{i}$  denotes the current tracking error between the Z and X terminals. The voltage transfer function of the proposed topology is given for the ideal case previously. Taking the non-idealities of ICCIIs given in Equation (5.5) into account, the transfer function is recalculated as follows;

$$\frac{V_{out}}{V_{in}} = \frac{Y_1(Y_2 - Y_3(1+\alpha)\beta)}{Y_2(Y_1 + Y_3(1+\alpha)(1+\beta))}.$$

(5.6)

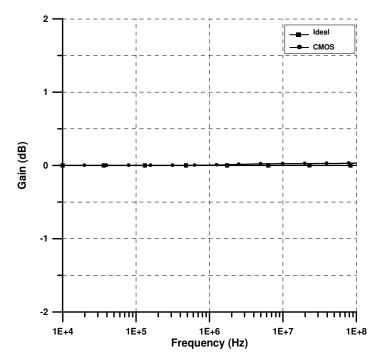

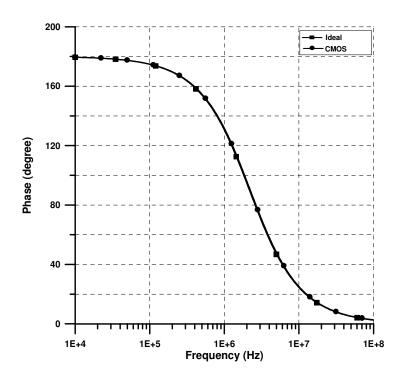

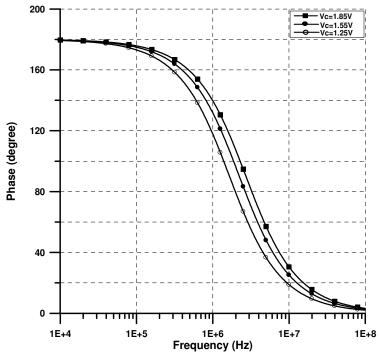

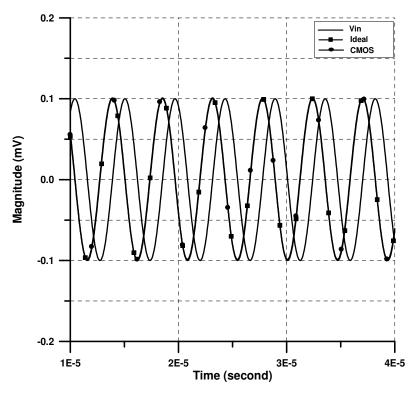

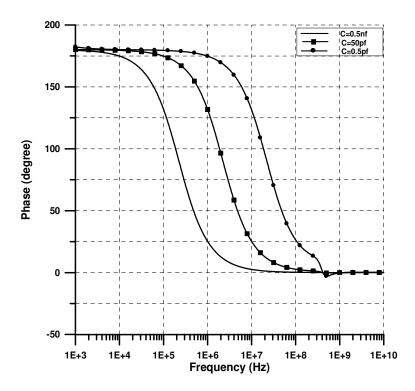

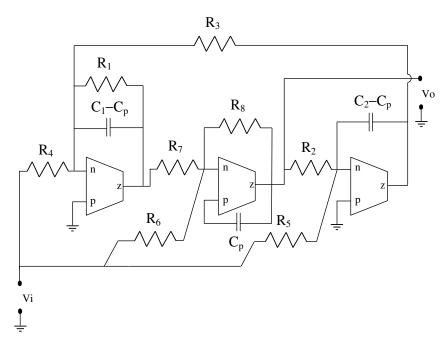

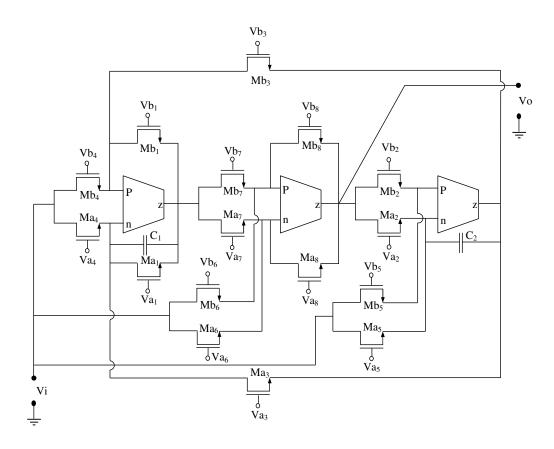

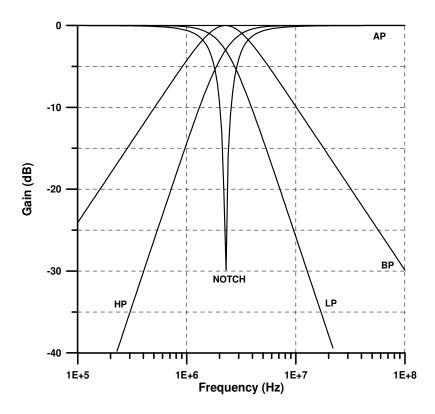

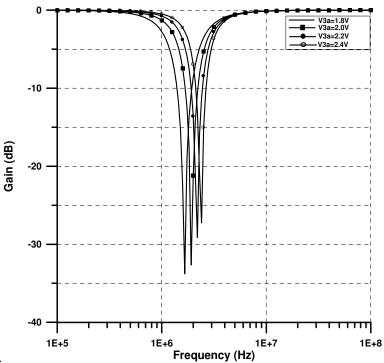

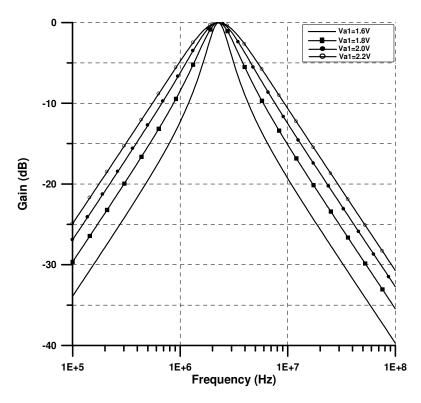

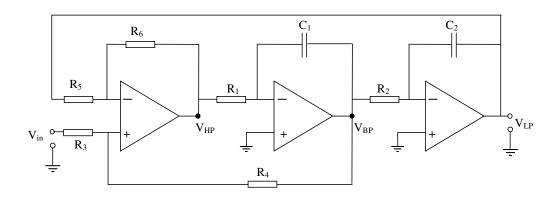

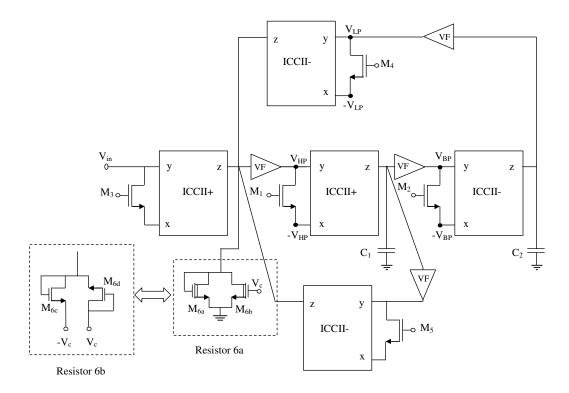

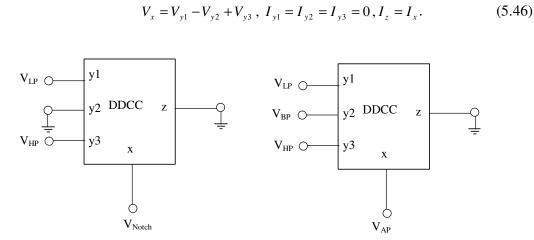

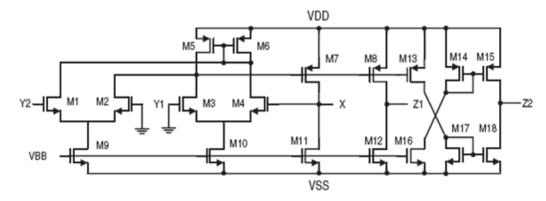

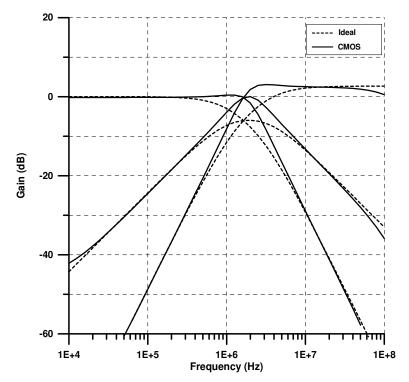

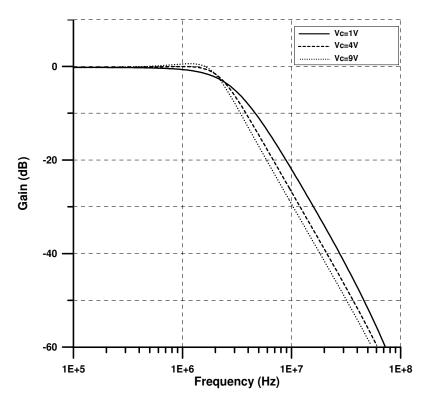

For eliminating non-ideal effects of the ICCII, the capacitance values must be chosen as  $Y_1 = ((1+\alpha).(1+\beta)).sC$  and  $Y_2 = ((1+\alpha).\beta).sC$ .