## DOKUZ EYLÜL UNIVERSITY GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

# ANALOG CIRCUIT DESIGN USING CURRENT AND TRANSRESISTANCE AMPLIFIERS

by Selçuk KILINÇ

> June, 2006 İZMİR

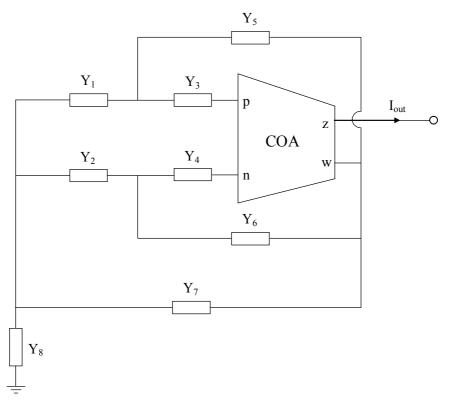

# ANALOG CIRCUIT DESIGN USING CURRENT AND TRANSRESISTANCE AMPLIFIERS

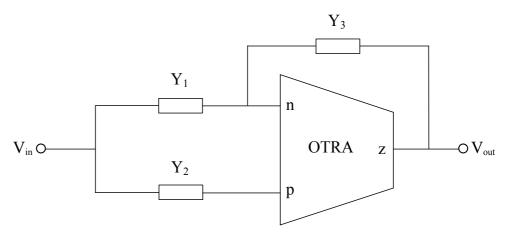

#### A Thesis Submitted to the

Graduate School of Natural and Applied Sciences of Dokuz Eylül University

In Partial Fulfillment of the Requirements for the Degree of Doctor of Philosophy in

Electrical and Electronics Engineering

by Selçuk KILINÇ

> June, 2006 İZMİR

#### Ph.D. THESIS EXAMINATION RESULT FORM

We have read this thesis entitled "ANALOG CIRCUIT DESIGN USING CURRENT AND TRANSRESISTANCE AMPLIFIERS" completed by Selçuk KILINÇ under supervision of Assoc. Prof. Dr. Uğur ÇAM and we certify that in our opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Doctor of Philosophy.

| Assoc                   | e. Prof. Dr. Uğur            | ÇAM                      |

|-------------------------|------------------------------|--------------------------|

|                         | Supervisor                   |                          |

| Prof. Dr. Haldun KARACA |                              | Prof. Dr. Erol UYAR      |

| Committee Member        |                              | Committee Member         |

| Prof. Dr. Hakan KUNTMAN |                              | Prof. Dr. Cüneyt GÜZELİŞ |

| Jury Member             |                              | Jury Member              |

|                         |                              |                          |

| Pro                     | f. Dr. Cahit HEL<br>Director | VACI                     |

Graduate School of Natural and Applied Sciences

#### **ACKNOWLEDGMENTS**

I would like to thank my supervisor Assoc. Prof. Dr. Uğur ÇAM for his valuable guidance and support during the course of this thesis. I wish to express my appreciation to Prof. Dr. Hakan KUNTMAN and Prof. Dr. Haldun KARACA for their useful comments. I am also grateful to the Scientific and Technical Research Council of Turkey, Münir Birsel Foundation for providing financial support during my Ph.D. studies. Finally, I sincerely thank my parents for their understanding and never ending support throughout my life.

Selçuk KILINÇ

### ANALOG CIRCUIT DESIGN USING CURRENT AND TRANSRESISTANCE AMPLIFIERS

#### **ABSTRACT**

Within the four amplifier types, voltage operational amplifier (op-amp) and operational transconductance amplifier (OTA) have been widely utilized in analog circuit design. On the other hand, the remaining two amplifiers, namely current operational amplifier (COA) and operational transresistance amplifier (OTRA), have not been received much attention until recently. However, the COA and OTRA have some advantageous properties that can be enjoyed by analog circuits. Both of them are characterized by internally grounded input terminals, leading to circuits that are insensitive to the stray capacitances. This feature also yields eliminating response limitations incurred by capacitive time constants. The output terminals of the COA are characterized by high impedance while the OTRA exhibits low output impedance. These make easy to drive loads without addition of a buffer for current mode and voltage mode circuits, which use COA and OTRA, respectively. The current differencing and internally grounded inputs of these elements make it possible to implement the circuits with MOS-C realization. In this thesis, two CMOS realizations for the COA are presented. They are basically obtained by cascading an OTRA and a dual output OTA. Current mode first order allpass filters, biquadratic filters and sinusoidal oscillators have been introduced as the applications of the CMOS COAs. Some analog circuits employing the OTRA have also been presented. Among these are first order allpass filters, all five different forms of second order filters, multifunction biquads, transimpedance type biquadratic filters and sinusoidal oscillators. OTRA based circuits for the realization of nth order voltage transfer function and fully controllable negative inductance are also included. The workability of the presented circuits has been verified by PSPICE simulation results. Some of the circuits are also tested experimentally.

**Keywords:** analog circuit design, integrated circuits, current operational amplifiers, operational transresistance amplifiers

#### AKIM VE GEÇİŞ-DİRENÇ KUVVETLENDİRİCİLER KULLANARAK ANALOG DEVRE TASARIMI

ÖZ

Dört kuvvetlendirici türü arasında, gerilim işlemsel kuvvetlendirici (op-amp) ve işlemsel geçiş-iletkenlik kuvvetlendirici (OTA), analog devre tasarımında yaygın olarak kullanılmaktadır. Diğer yandan, geriye kalan iki kuvvetlendirici, yani akım islemsel kuvvetlendirici (COA) ve islemsel geçiş-direnç kuvvetlendirici (OTRA), son zamanlara kadar fazla ilgi çekmemiştir. Bununla birlikte, COA ve OTRA, analog devreler tarafından kullanılabilecek olan bazı avantajlı özelliklere sahiptir. Her ikisi de içten topraklı giriş uçları ile karakterize edildiğinden kaçak kapasitelere duyarsız devrelere yol açarlar. Aynı zamanda bu özellik, kapasitif zaman sabitleri nedeniyle oluşan cevap sınırlamalarını yok eder. COA'nın çıkış uçları yüksek empedans olarak karakterize edilmekte, OTRA ise alçak empedans çıkış ucu sergilemektedir. Bu durum, COA kullanan akım modlu ve OTRA kullanan gerilim modlu devrelerde, bağlanacak yüklerin tampon devresi eklenmeksizin sürülmesini kolaylaştırır. Bu elemanların akım farkı alan ve içten topraklı olan girişleri, devrelerin MOS-C olarak gerçeklenmesini mümkün kılar. Bu tezde, COA için iki CMOS gerçeklemesi sunulmuştur. Bunlar temelde bir OTRA ile çift çıkışlı bir OTA'nın art arda bağlanmasıyla elde edilmiştir. CMOS COA'ların uygulamaları olarak, akım modlu birinci derece tüm geçiren filtreler, ikinci derece filtreler ve sinüsoidal osilatörler tanıtılmıştır. OTRA kullanan bazı analog devreler de sunulmuştur. Bunlar arasında, birinci derece tüm geçiren filtreler, bütün beş ayrı türdeki ikinci derece filtreler, çok fonksiyonlu filtreler, geçiş-empedans tipindeki filtreler ve sinüsoidal osilatörler yer almaktadır. Ayrıca, n. dereceden gerilim transfer fonksiyonu ve tümüyle kontrol edilebilen negatif endüktans gerçeklemeleri için OTRA tabanlı devreler içerilmektedir. Sunulan devrelerin çalışabilirliği, PSPICE benzetim sonuçlarıyla gösterilmiştir. Devrelerin bazıları deneysel olarak da test edilmiştir.

**Anahtar Kelimeler:** analog devre tasarımı, tümdevreler, akım işlemsel kuvvetlendirici, işlemsel geçiş-direnç kuvvetlendirici

#### **CONTENTS**

|          |                                               | Page |

|----------|-----------------------------------------------|------|

| THESIS F | EXAMINATION RESULT FORM                       | ii   |

|          | VLEDGEMENTS                                   |      |

|          | CT                                            |      |

|          |                                               |      |

|          | TS                                            |      |

| СНАРТЕ   | CR ONE – INTRODUCTION                         | 1    |

| 1.1      | Analog Circuit Design                         | 1    |

| 1.2      | Integrated Circuit Technologies               |      |

| 1.3      | Current Mode Approach                         | 4    |

| 1.4      | Current Mode Building Blocks                  | 7    |

| 1.5      | Current and Tranresistance Amplifiers         | 9    |

| 1.6      | Thesis Outline                                | 11   |

| СНАРТЕ   | CR TWO – CURRENT AND TRANSRESISTANCE AMPLIFIE | RS12 |

| 2.1      | Ideal Amplifier                               | 12   |

| 2.2      | Reciprocity and Adjoint Networks              | 13   |

| 2.3      | Classification of Amplifiers                  | 15   |

| 2.4      | Closed Loop Amplifier Performance             | 18   |

| 2.5      | Current Operational Amplifier                 | 20   |

| 2.6      | Operational Transresistance Amplifier         | 23   |

| СНАРТЕ   | CR THREE – CMOS REALIZATION EXAMPLES FOR COA  | 26   |

| 3.1      | Block Diagram Model of the COA                | 26   |

| 3.2      | Implementation of COA Using Current Conveyors | 27   |

| 3.3      | The First Example of CMOS COA Realization     | 31   |

| 3.4      | The Second Example of CMOS COA Realization    | 35   |

| CHAPTE | R FOUR – ANALOG CIRCUIT DESIGN USING COA                   | 39  |

|--------|------------------------------------------------------------|-----|

| 4.1    | Current Mode First Order Allpass Filters                   | 39  |

| 4.2    | Current Mode Biquadratic Filters                           | 45  |

| 4.3    | Current Mode Sinusoidal Oscillators                        | 54  |

| СНАРТЕ | R FIVE – ANALOG CIRCUIT DESIGN USING OTRA                  | 60  |

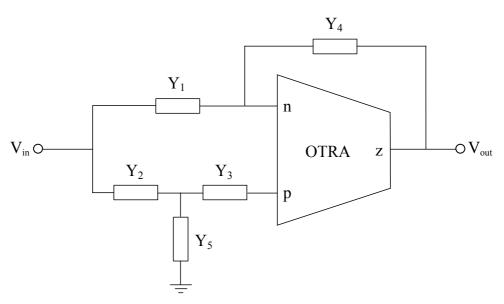

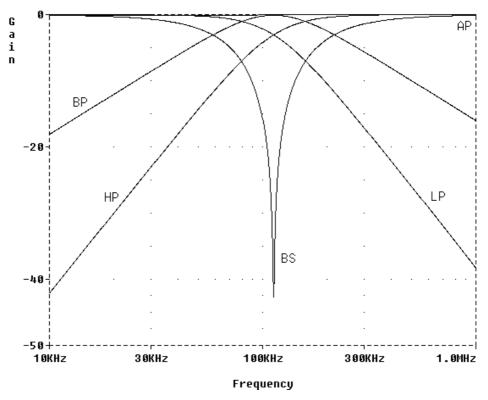

| 5.1    | Allpass and Notch Filters                                  | 60  |

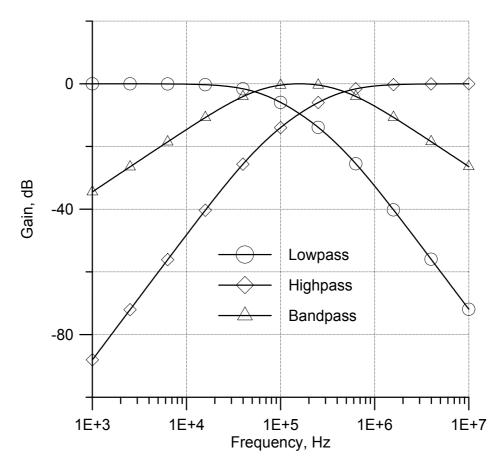

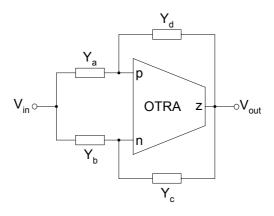

| 5.2    | Lowpass, Highpass and Bandpass Biquads                     | 69  |

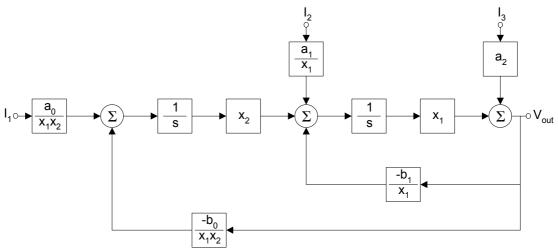

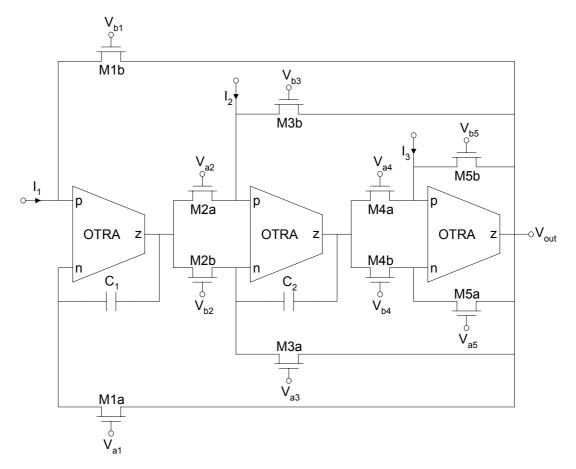

| 5.3    | Realization of <i>n</i> th Order Voltage Transfer Function | 72  |

| 5.4    | Multifunction Biquads                                      | 80  |

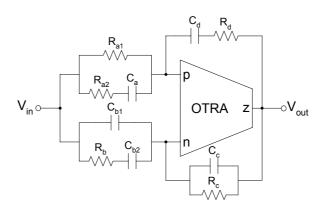

| 5.5    | Transimpedance Type Fully Integrated Biquadratic Filters   | 84  |

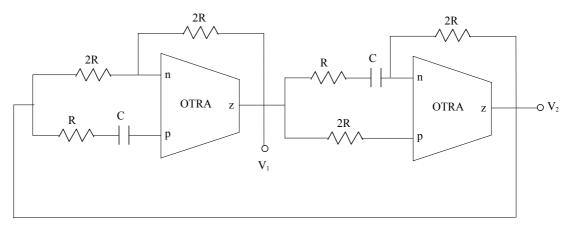

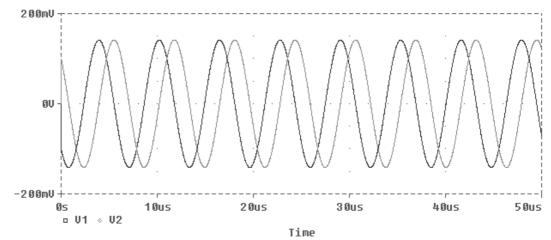

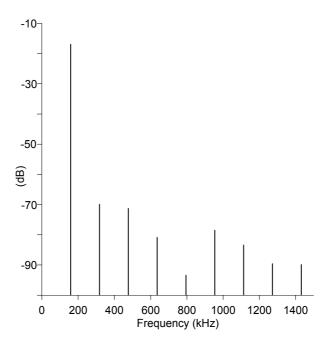

| 5.6    | Sinusoidal Oscillators                                     | 93  |

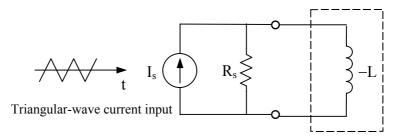

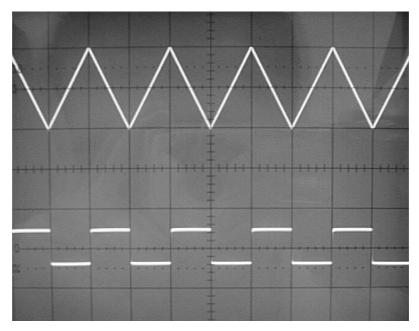

| 5.7    | Realization of Fully Controllable Negative Inductance      | 95  |

| СНАРТЕ | R SIX – CONCLUSION                                         | 106 |

| 6.1    | Concluding Remarks                                         | 106 |

| 6.2    | Future Work                                                | 107 |

| DEFEDE | NCES                                                       | 108 |

### CHAPTER ONE INTRODUCTION

#### 1.1 Analog Circuit Design

Analog circuit design is the successful implementation of analog circuits and systems using integrated circuit (IC) technology. Analog circuits and systems have an important role in the implementation and application of very large scale integration (VLSI) technology. The development of VLSI technology, coupled with the demand for more signal processing integrated on a single chip, has resulted in an increased need for the design of effective analog ICs (Allen & Holberg, 1987). Analog circuit design is becoming increasingly important with growing opportunities. The emergence of ICs incorporating mixed analog and digital functions on a single chip has led to an advanced level of analog design (Toumazou, Lidjey & Haigh, 1990).

Since the early 1970's, the field of analog circuits and systems has developed and matured. During this period, much has been made of the competition between analog and digital system design strategies. Advances in digital VLSI have enabled memories, microprocessors, and digital signal processors (Laker & Sansen, 1994). As the level of integration increased in IC technology, digital circuit implementation became more desirable than analog circuit implementation. This is because of its robustness, reliability, accuracy, ease of design, programmability, flexibility, and cost (Toumazou et al., 1990). With the advances of VLSI technology, digital signal processing is proliferating and penetrating into more and more applications. Many applications which have been traditionally implemented in analog domain have been moved to digital, such as digital audio and wireless cellular phones (Allen & Holberg, 1987).

Even if digital circuits could always outperform analog circuits with smaller or equivalent area, analog circuits would still be required (Toumazou et al., 1990). There are some facts that make analog ICs and systems increasingly important. First

of all, the natural world is analog. Thus, analog systems are needed in information acquisition systems in order to prepare analog information for conversion to digital format (Laker & Sansen, 1994). In other words, interface functions are required between the real world and the silicon system due to the fact that most of the signals in the physical world are analog. The primary information acquired from the real world is usually in the form of time continuous analog signals and must be interfaced to digital circuitry. The result of the digital processing must likewise be converted to back to analog form. In a digital signal processing system, amplification, filtering, and signal conditioning are required before converting to the digital format. After output signal digital to analog conversion, again filtering is needed. Finally, the smoothed output signal must be amplified to the appropriate power level to achieve the desired effect (Toumazou et al., 1990). That is, analog pre-processing before the analog to digital conversion and post-processing after the digital to analog conversion are needed for a digital signal processing system. Therefore, analog circuits will continue to be a part of large VLSI digital systems (Allen & Holberg, 1987).

In recent years, the quest for ever smaller and cheaper electronic systems has led manufacturers to integrate entire system onto a single chip. It is now becoming common to find that a single mixed analog and digital (mixed mode) IC contains both a digital signal processor and all the analog interface circuits required to interact with its external analog transducers and sensors (Aaserud & Nielsen, 1995). That is, analog and digital VLSI circuits coexist on the same chip (Laker & Sansen, 1994). On the other hand, there remain many signal processing tasks that are best performed by analog circuits. Complete analog systems will still continue to be required in some applications, mainly those in which the frequency of operation is too high for digital implementation or in very low power applications (Aaserud & Nielsen, 1995).

#### 1.2 Integrated Circuit Technologies

The element of principal importance concerning analog signal processing is the trend of technology. There are mainly four viable integrated technologies for analog

circuits. These technologies are bipolar, complementary metal oxide semiconductor (CMOS), BiCMOS, and gallium arsenide (GaAs) (Toumazou et al., 1990). Much of the analog design during the 1960's and 1970's was done in bipolar technology. The 1980's was an era of rapid evolution of MOS analog ICs, in particular CMOS (Laker & Sansen, 1994).

CMOS technology has become a dominant analog technology primarily because of good quality capacitors, good switches and low power dissipation (Toumazou et al., 1990). It provides very large scale integration of both high density digital circuits and analog circuits for low cost. On the other hand, comparison between the bipolar and CMOS technologies in terms of bandwidth and noise favors the bipolar from an analog viewpoint. However, a similar comparison made from a digital viewpoint would come up on the side of CMOS. Therefore, since large volume technology will be driven by digital demands, CMOS is an obvious result as the technology of availability. Furthermore, the potential for technology improvement for CMOS is greater than for bipolar and the performance in CMOS generally increases with decreasing channel length (Allen & Holberg, 1987).

During the 1990's, we have seen the BiCMOS technology emerge as a serious contender to the original technologies (Laker & Sansen, 1994). BiCMOS technology combines both bipolar and CMOS technologies and obviously has the advantages of both. BiCMOS offers the ability of low power dissipation using CMOS and high speed performance using bipolar (Toumazou et al., 1990). On the other hand, it is somewhat more expensive to fabricate. GaAs technology is quickly maturing and offers many possibilities as a niche technology. From an analog viewpoint, GaAs is well developed for microwave analog but less developed for analog signal processing (Toumazou et al., 1990).

It is clear that CMOS technology is preferred for digital design. Since analog and digital functions are placed onto a single chip in modern VLSI systems, the use of CMOS technology for analog circuits is also preferred. CMOS process implementation is preferable because CMOS process makes it possible to implement

mixed signal circuit chips with lower cost (Takagi, 2001). During the past years, we have seen a proliferation of mixed analog/digital VLSI ICs realized in state of the art CMOS technologies to optimize cost and power dissipation in consumer products, many of which are pocket size and battery powered (Laker & Sansen, 1994). It has also the advantages of low power consumption and high integration density. Therefore, dominant VLSI technology for analog circuits is CMOS up to GHz range.

#### 1.3 Current Mode Approach

Analog processing systems traditionally use input and output voltages which are in charge of carrying the information. The voltage – current duality, which results from the Kirchoff's laws, as well as from the Thevenin's and Norton's theorems, allows analog circuits working from current signals to be obtained, too. Because the measurement of a voltage across an impedance was easier than the measurement of the current flowing through this impedance, engineers used to work with voltages rather than with currents (Fabre, 1995a). Thus, it has become customary in electrical engineering to think of signal processing in terms of voltage variables rather than current variables. This tendency has resulted in voltage signal processing circuits such as voltage amplifiers, voltage integrators, filters which realize a voltage transfer function, etc (Allen & Terry, 1980).

Most analog signal processing is accomplished through the use of feedback around a high gain voltage amplifier to achieve a well defined voltage transfer function which is independent of the active devices. The high gain voltage amplifier may consist of discrete components or may be an IC such as a voltage operational amplifier (op-amp). This approach has worked well as evidenced by a large number of analog circuits which use the voltage op-amp (Allen & Terry, 1980).

Since the introduction of ICs, the op-amp has served as the basic building block in analog circuit design and has been widely used in a variety of applications such as addition/subtraction circuits, amplifiers, multipliers/dividers, interface circuitry, digital to analog converters, analog to digital converters, variable gain amplifiers,

filters, oscillators, etc (Koli, 2000). Most of the systems based on voltage op-amps represent the signal of interest in the voltage domain (Youssef & Soliman, 2005).

High frequency operation is an ever present demand on analog circuits. Analog circuits are always requested to work at high frequencies where digital signal processing faces difficulties with implementation. In addition to this demand, a recent advanced fabrication process forces analog circuits to operate under supply voltages as low as possible. This is because of reduction in tolerant voltages of transistors, reduction in power consumption, the same chip implementation together with digital circuits, etc (Takagi, 2001). In these respects, realization of low voltage and high frequency analog circuits is one of the most attractive and important issues in many signal processing fields.

However, the classical op-amp suffers from limited gain-bandwidth product problems and from low slew rate at its output. Many circuits employing op-amps have been designed and described. The limited gain-bandwidth product of the op-amp affects the parameters of the circuits designed. They remain, therefore, unsatisfactory at higher frequencies (Budak, 1974).

In order to correspond to the severe demands for high frequency and low power supply voltage operation on analog circuits, designers made plenty of attempts. Among these is the current mode approach. There has been a great shift in analog circuit design towards representing signals with current instead of voltage to achieve high performance analog circuits in CMOS technology. So, in the past years current mode circuits began to receive a great attention as a new alternative to voltage mode circuits. This is because one of the most promising solutions to high frequency and low voltage operation is thought to be current signal processing (Takagi, 2001). A current mode circuit may be taken to mean any circuit in which current is used as the active variable in preference to voltage, either throughout the whole circuit or only in certain critical areas (Wilson, 1990).

Current mode circuits have been receiving considerable attention due to their potential advantages such as inherently wide bandwidth, higher slew rate, wider dynamic range, simpler circuitry, low voltage operation and low power consumption (Toumazou et al., 1990). Furthermore, current mode circuits are suitable for integration with CMOS technology and thus have become more and more attractive in electronic circuit design in recent years (Toker, Kuntman, Çiçekoğlu & Dişçigil, 2002).

Transistors are more suitable for processing currents rather than voltages because they are inherently current mode i.e., both bipolar and MOS transistors are current output devices. An important number of elementary mathematical functions can be obtained easier from current signals rather than from voltage. In this order, to generate the sum of various currents flowing to ground does not necessitate to use any passive components. This can easily be obtained onto any virtually grounded node. On the contrary, summing several voltages is not as easy. The later needs several resistances to achieve respectively both voltage-current conversion on input and current-voltage conversion on output. The operation of summation being also obtained as before, from current signals (Fabre, 1995a). Therefore, mathematical operations of adding, subtracting or multiplying signals represented by currents are simpler to perform than when they are represented by voltages. For this reason, integrated current mode system realizations are closer to the transistor level than the conventional voltage mode realizations and therefore simpler circuits and systems should result (Koli, 2000).

In voltage mode circuits the high valued resistors with parasitic capacitances create a dominant pole at a relative low frequency, which limits the bandwidth. In general, the node impedances in current mode circuits are low and the voltage swings are small. Thus the time constant is reduced and also the time required for charging and discharging a parasitic capacitor is kept small. Hence the slew rate for current mode circuits will be sufficiently high. They are well suited to work at higher frequencies and thus are often used in communication circuits (Toker et al., 2002).

The low supply voltage operation is achieved because small voltages appear on the nodes.

From these major merits many analog circuit designers believe that current mode circuit techniques meet the severe demands for low power supply voltage and high frequency operation on analog circuits. Although a current mode approach is promising, voltage mode circuits have a lot of merits against current mode circuits. First of all, a fact that there exist plenty of practically used circuits is very important in terms of reliability. Because of this, most of the systems use not current signals but voltage signals. Therefore, a voltage mode approach is still attractive even though a current mode one becomes popular (Takagi, 2001).

#### 1.4 Current Mode Building Blocks

To overcome the certain limitations of op-amp in analog circuits, many new building blocks that are suitable for current mode circuits have been introduced. Among these current conveyors are very famous.

The concept of the current conveyor was first presented in 1968 (Smith & Sedra, 1968) and further developed to a second generation current conveyor in 1970 (Sedra & Smith, 1970). The current conveyor is intended as a general building block as with the op-amp. On the other hand, neither of these building blocks became popular as a consequence of the introduction of the integrated op-amp at the time. Because of the op-amp concept has been current since the late 1940's, it is difficult to get any other similar concept widely accepted. Additionally, integrated current conveyors were difficult to realize due to the lack of high performance integration technologies in the 1970's. During the 1980's, research societies started to notice that the voltage op-amp is not necessarily the best solution to all analog circuit design problems. Voltage op-amps do not perform well in applications where a current output signal is needed and consequently there is an application field for current conveyor circuits. Since current conveyors operate without any global feedback, a different high frequency behavior compared to op-amp circuits results (Koli, 2000).

In many applications, only one of the virtual grounds in the input terminals of the first generation current conveyor is used and the unused terminal must be grounded or otherwise connected to a suitable potential. This grounding must be done carefully since a poorly grounded input terminal may cause an unwanted negative impedance at the other input terminal. Moreover, for many applications a high impedance input terminal is preferable. For these reasons, the second generation current conveyor was developed. It has one high and one low impedance input rather than the two low impedance inputs of the first generation current conveyor. Yet another current conveyor was proposed in 1995 (Fabre, 1995b). The operation of the third generation current conveyor is similar to that of the first generation current conveyor, with the exception that the currents in the input terminals flow in opposite directions. This current conveyor can be used as an active current probe (Koli, 2000).

Furthermore, a commercial product, the current feedback operational amplifier, became available. The high slew rate and wide bandwidth of this amplifier resulted in its popularity in video amplifier applications. It provides the advantage of having constant bandwidth irrespective of the gain as oppose to classical op-amp. It is also used in voltage mode operation as well as in current mode. The current feedback operational amplifier is in effect a positive second generation current conveyor with an additional voltage buffer at the conveyor current output. The current at the inverting input of the current feedback operational amplifier is transferred to the high impedance current conveyor output, causing a large change in output voltage (Koli, 2000).

There are some other additional types of building blocks as the variations of the current conveyors such as; differential voltage current conveyor, differential difference current conveyor, controlled current conveyor, inverting current conveyor, operational floating conveyor, current differencing buffered amplifier (CDBA), etc. Most of these elements are unity gain amplifiers. There are many applications of these building blocks both in voltage mode and current mode operation.

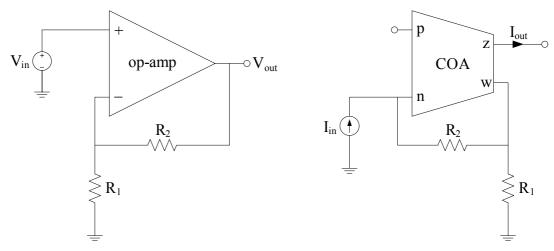

#### 1.5 Current and Transresistance Amplifiers

In general, amplifiers are classified into four groups as voltage op-amp, current operational amplifier (COA), operational transconductance amplifier (OTA) and operational transresistance amplifier (OTRA). The voltage op-amp and the OTA have been widely used in several applications for many years, whereas the COA and the OTRA have not gained much attention until recently. The four devices can be arranged into two dual pairs according to adjoint networks principle (Bordewijk, 1956; Tellegen, 1952). The voltage op-amp and the COA form one pair, while the OTA and the OTRA constitute the other pair (Payne & Toumazou, 1996).

One of the most popular methods for transformation between the current domain and the voltage domain in analog signal processing is the principle of adjoint networks. Using this principle, any voltage mode circuit based on the op-amp can be transformed to a current mode circuit using the COA (Bruun, 1994). The same transformation is possible between the circuits that employ the OTA and the OTRA.

The COA is basically a differential current-controlled current source with a very high, ideally infinite, current gain. It exhibits very low, ideally zero, input resistances and very high, ideally infinite, output resistances.

As mentioned before, the COA is the current mode counterpart of the conventional voltage op-amp and it is particularly suitable in transforming op-amp based voltage mode circuits into their current mode equivalents. Since the voltage op-amp has been used in wide range of applications operating in voltage mode for a long time, its current mode counterpart, COA, seems to be the suitable candidate as the active element of current mode circuits. Applying the adjoint networks theorem to traditional designs based on voltage op-amps such as; amplifiers, integrators, filters, etc. will result in current mode circuits performing the same function but based on the COA.

Many of these current mode circuits can also be implemented using current conveyors as the basic active building block. However, since the current conveyors are unity gain elements, the transfer functions of the circuits are sensitive to the current tracking errors of the current conveyors. It is a well known fact that open loop circuits are less accurate compared to their high gain counterparts. On the other hand, the COA is a high gain current-input, current-output device. Using this device in negative feedback configuration makes it possible to obtain very accurate transfer functions, essentially independent of its inaccurate open loop gain (Mucha, 1995). Therefore, the COA seems to be the true current mode active element for current mode circuits.

The applications of the COA include the implementation of instrumentation amplifier (Yen & Gray, 1982), current comparator with hysteresis (Laopoulos, Siskos, Bafleur, Givelin & Tornier, 1995), gyrator (Mucha, 1995), differential switched current filter (Cheng & Wang, 1998; Zele, Allstot & Fiez, 1991), and variable gain amplifiers (Youssef & Soliman, 2005). The COA is also used in biomedical, industrial and aerospace applications (Wang, 1990). In addition, it is particularly suitable for temperature sensors, photo sensors and, in general, whenever the input source and/or the output are current signals (Kauert, Budde & Kalz, 1995; Van den Broeke & Nieuwkerk, 1993; Vanisri & Toumazou, 1992). A current amplifier can be also arranged in a true multi-output fashion, since several current output stages can be embedded. Finally, an interesting and almost unique property of current amplifiers is their feasibility for nonlinear resistances in the feedback network, thanks to the fact that the voltage drop across them is the same (Magram & Arbel, 1994; Palmisano, Palumbo & Pennisi, 2000).

The OTRA is basically a differential current-controlled voltage source with a very high, ideally infinite, transresistance gain. It exhibits very low, ideally zero, input and output resistances.

The OTRA is also known as current differencing amplifier or Norton amplifier. It was used in some applications, including filter realizations, in the late 1970's and the

early 1980's (Anday, 1977a; Anday, 1977b; Anday, 1982; Brodie, 1978). Although the OTRA is commercially available from several manufacturers, it has not gained much attention until recently. These commercial realizations have certain drawbacks. On the other hand, in recent years, several high performance CMOS OTRA realizations have been presented in the literature (J. J. Chen, Tsao & C. C. Chen, 1992; Salama & Soliman, 1999a). This leads to growing interest for the design of OTRA based analog signal processing circuits. The OTRA has been used in the realization of filters (Salama & Soliman, 1999a), oscillators (Çam, 2002; Salama & Soliman, 2000), and variable gain amplifiers (Elwan, Soliman & Ismail, 2001).

#### 1.6 Thesis Outline

The main objective of this thesis is to introduce new analog circuits using the COA and OTRA. Chapter 2 presents the classification of amplifiers and gives the properties of COA and OTRA. Block diagram representations and CMOS realizations of the COA are given in Chapter 3. Current mode first order allpass filters, biquadratic filters and sinusoidal oscillators that are all employ a single COA as the active element are included in Chapter 4. Chapter 5 presents many new OTRA based circuits including allpass and notch filters; lowpass, highpass and bandpass biquads; high order filters; transimpedance type filters; sinusoidal oscillators and negative inductance simulators. Concluding remarks are given in Chapter 6.

#### **CHAPTER TWO**

#### **CURRENT AND TRANSRESISTANCE AMPLIFIERS**

#### 2.1 Ideal Amplifier

In 1954, Tellegen introduced the concept of an "ideal element" or "ideal amplifier" (Tellegen, 1954) as a general building block for the implementation of linear and nonlinear analog systems. This ideal device was a two-port with four associated variables  $-V_1$ ,  $I_1$  at the input port and  $V_2$ ,  $I_2$  at the output port. When represented geometrically in 4-D space the device could be defined by the planes  $V_1 = 0$ ,  $I_1 = 0$  and  $V_2$ ,  $I_2$  arbitrary. The amplifier would therefore exhibit an infinite power gain between the input and output ports (Payne & Toumazou, 1996).

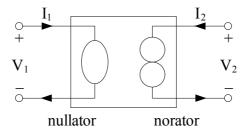

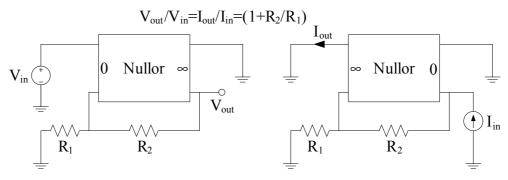

In 1964, Carlin proposed the concept of the "nullor" (Carlin, 1964), which was a two-port comprising an input nullator and an output norator, as shown in Figure 2.1. The port voltage and current of a nullator are always zero, while the port voltage and current of a norator can independently take any value; both components therefore have an undefined impedance. The nullor satisfies the definition of an ideal amplifier as given by Tellegen (Payne & Toumazou, 1996).

Figure 2.1 The nullor

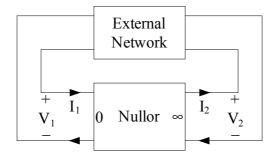

As an electrical circuit component, the transfer properties of the nullor only become well defined if an external network provides for feedback from the output to the input port, as shown in Figure 2.2. The output variables  $(V_2, I_2)$  will then be determined by the external network in such a way that the input conditions  $(V_1 = 0, I_1 = 0)$  are satisfied (Payne & Toumazou, 1996).

Figure 2.2 Nullor with feedback network

Depending on the nature of the external feedback network, many linear and nonlinear analog transfer functions can be implemented. In addition, the external network can usually be chosen such that the resulting transfer function is independent of any source or load. The nullor is thus particularly suitable for separating two stages of an analog system which are mismatched in terms of impedance, thereby eliminating loading effects and allowing stages to be easily cascaded (Payne & Toumazou, 1996).

#### 2.2 Reciprocity and Adjoint Networks

Tellegen's Reciprocity Theorem (Tellegen, 1952) defines a network as reciprocal if the same transfer function is obtained when the input excitation and output response are interchanged. Many useful network theorems can be derived from the principle of reciprocity, which facilitate, for example, the calculation of energy distribution and dissipation and network sensitivities (Penfield, Spence & Duinker, 1970). A network which satisfies the definition of reciprocity is always composed of components which are themselves reciprocal (generally passive elements such as resistors, capacitors, inductors). Networks containing active components generally do not satisfy the criteria for reciprocity, so Bordewijk (1956) extended the scope of the theorem by defining the concept of inter-reciprocity. Two networks are said to be inter-reciprocal if they jointly satisfy the condition of reciprocity; that is, if the two networks give the same transfer function under an interchange of excitation and response. Clearly any reciprocal network will be inter-reciprocal with itself (Payne & Toumazou, 1996).

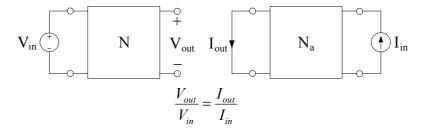

Figure 2.3 Inter-reciprocal networks N and N<sub>a</sub>

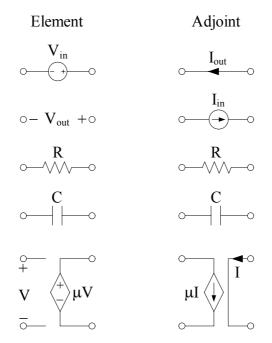

Figure 2.4 Circuit elements and their adjoints

An inter-reciprocal network N<sub>a</sub> is known as the "adjoint" of the original network N (see Figure 2.3). Since a network and its adjoint are inter-reciprocal, they are exactly equivalent in terms of signal transfer, sensitivity, power dissipation, etc. The properties of the adjoint network can therefore be inferred from the properties of the original, without requiring any further analysis. The adjoint network can be found by following rules given by Tellegen (1951), and summarized by Director & Rohrer (1969); first construct a replica of the original network, then go through this replica, replacing each element with its adjoint (see Figure 2.4). A resistor is left alone (that is, it is replaced by itself), and similarly capacitors and inductors are left alone. A voltage source becomes a short circuit (and vice versa), while a current source is replaced by an open circuit (and vice versa). Following these rules, a nullor is replaced by a nullor, but with the input and output ports interchanged (thus the

nullor is "self inter-reciprocal" or "self adjoint"). Adjoint networks are also known as "dual" networks, since they are equivalent under an interchange of voltage and current signals. Figure 2.5 illustrates the adjoint network principle (Payne & Toumazou, 1996).

Figure 2.5 Adjoint (inter-reciprocal) networks

#### 2.3 Classification of Amplifiers

The nullor is the most general case of a universal ideal amplifier, but in practice the undefined input and output resistance levels make this device difficult to implement. Tellegen (1954) recognized this problem and proposed a set of four ideal amplifiers, each with a well defined input resistance ( $R_{in}$ ) and output resistance ( $R_{out}$ ). These four ideal amplifiers are (see Figure 2.6) (Payne & Toumazou, 1996):

- The Voltage Amplifier or Voltage-Controlled Voltage Source (VCVS). This device has an open circuit input port  $(R_{in} = \infty)$ , a short circuit output port  $(R_{out} = 0)$ , and an open loop voltage gain  $(V_2 = A \ V_1)$ .

- The Current Amplifier or Current-Controlled Current Source (CCCS). This device has a short circuit input port  $(R_{in} = 0)$ , an open circuit output port  $(R_{out} = \infty)$ , and an open loop current gain  $(I_2 = B I_1)$ .

- 3) The Transconductance Amplifier or Voltage-Controlled Current Source (VCCS).

This device has open circuit input and output ports  $(R_{in} = R_{out} = \infty)$ , and an open loop transconductance gain  $(I_2 = G_m V_I)$ .

4) The Transresistance Amplifier or Current-Controlled Voltage Source (CCVS).

This device has short circuit input and output ports  $(R_{in} = R_{out} = 0)$ , and an open loop transresistance gain  $(V_2 = R_m I_1)$ .

| Device                                             | Symbol                                                    | Relationship                                                                                                                           |  |

|----------------------------------------------------|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| Voltage-<br>controlled<br>voltage source<br>(VCVS) | $V_1$ $AV_1$ $V_2$                                        | $\begin{bmatrix} I_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ A & 0 \end{bmatrix} \begin{bmatrix} V_1 \\ I_2 \end{bmatrix}$     |  |

| Current-<br>controlled<br>current source<br>(CCCS) | $I_1$ $BI_1$                                              | $\begin{bmatrix} V_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ B & 0 \end{bmatrix} \begin{bmatrix} I_1 \\ V_2 \end{bmatrix}$     |  |

| Voltage-<br>controlled<br>current source<br>(VCCS) | $V_1$ $G_mV_1$                                            | $ \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ G_m & 0 \end{bmatrix} \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} $ |  |

| Current-<br>controlled<br>voltage source<br>(CCVS) | $\begin{matrix} & & & & & & & \\ & & & & & & \\ & & & & $ | $ \begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} 0 & 0 \\ R_m & 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} $ |  |

Figure 2.6 The ideal amplifier set

For each amplifier, the available power gain is infinite, and the output voltage or output current is directly proportional to the input voltage or input current, independent of any loading effects. Each amplifier differs from the nullor in the respect that they are no longer "self inter-reciprocal"; however they can be arranged into dual or adjoint pairs. The ideal voltage and current amplifiers form one dual pair provided that A = B and the input and output ports are interchanged, and the ideal transconductance and transresistance amplifiers form another dual pair

provided that  $G_m = R_m$ , and the input and output ports are interchanged (Payne & Toumazou, 1996).

The amplification of signals is perhaps the most fundamental operation in analog signal processing, and in the early days amplifier circuit topologies were generally optimized for specific applications. However the desirability of a general purpose high gain analog amplifier was recognized by system designers and IC manufacturers alike, since the application of negative feedback allows many analog circuit functions (or "operations") to be implemented accurately and simply. A general purpose device would also bring economies of scale, reducing the price and allowing ICs to be used in situations where they may have previously been avoided on the basis of cost. "Operational amplifiers" (op-amps) were thus featured among the first generation of commercially available ICs (Payne & Toumazou, 1996).

Of the four amplifier types described by Tellegen, the voltage op-amp (VCVS) has emerged as the dominant architecture almost to the exclusion of all others, and this situation has a partly historical explanation. Early high gain amplifiers were implemented using discrete thermionic valves which were inherently voltage-controlled devices, and a controlled voltage output allowed stages to be easily cascaded. The resulting voltage op-amp architectures were translated to silicon with the development of IC technologies, and the device has since become ubiquitous to the area of analog signal processing. The architecture of the voltage op-amp has several attractive features; for example, the differential pair input stage is very good at rejecting common mode signals. In addition a voltage op-amp only requires a single ended output to simultaneously provide negative feedback and drive a load, and the implementation of a single ended output stage is a much simpler task than the design of a fully differential or balanced output (Payne & Toumazou, 1996).

On the negative side, the architecture of the voltage op-amp produces certain inherent limitations in both performance and versatility. The performance of the voltage op-amp is typically limited by a fixed gain-bandwidth product and a slew rate whose maximum value is determined by the input stage bias current. The

versatility of the voltage op-amp is constrained by the single ended output, since the device cannot be easily configured in closed loop to provide a controlled output current (this feature requires the provision of a differential current output). The voltage op-amp is therefore primarily intended for the implementation of closed loop voltage processing (or "voltage mode") circuits, and as a result most analog circuits and systems have been predominantly voltage driven. Since it is often desirable to maximize signal swings while minimizing the total power consumption, voltage mode circuits generally contain many high impedance nodes to minimize the total current consumption (Payne & Toumazou, 1996).

#### 2.4 Closed Loop Amplifier Performance

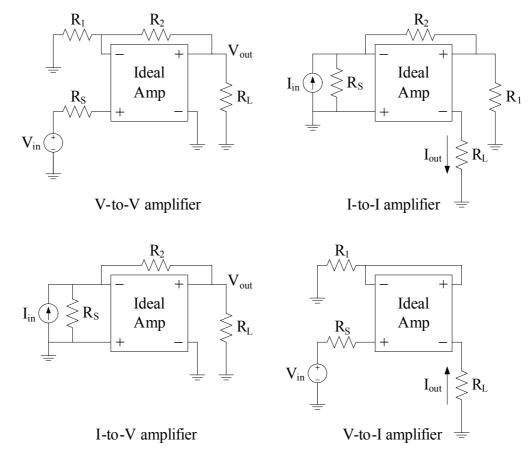

The differing levels of input and output resistance among the various amplifier types suggests that each might perform differently when presented with the same external network. To investigate this further we return to Tellegen's ideal amplifier set (VCVS, CCCS, VCCS, CCVS), and derive the transfer functions obtained when each amplifier is configured in turn to implement the various closed loop functions shown in Figure 2.7 (Payne & Toumazou, 1996).

These circuits are chosen for the varying combinations of input source and output drive which they impose on the ideal amplifier. The transfer functions for these circuits are obtained by replacing the ideal amplifier by each of the specific types (Payne & Toumazou, 1996).

There are four possible types of closed loop amplifiers which differ in the combinations of input source an output drive as voltage to voltage (V-V) amplifier, current to current (I-I) amplifier, current to voltage (I-V) amplifier, and voltage to current (V-I) amplifier. The closed loop configurations for each kind of amplifier are illustrated in Figure 2.7, where the symbol of the ideal amplifier was used. Table 2.1 summarizes the transfer functions which result for each kind of feedback amplifier (Palmisano, Palumbo & Pennisi, 1999).

Figure 2.7 Closed loop amplifier applications

Table 2.1 Transfer functions of amplifiers in Figure 2.7

| V-V amplifier | I-I amplifier | I-V amplifier  | V-I amplifier |

|---------------|---------------|----------------|---------------|

| $1+R_2/R_1$   | $1+R_2/R_1$   | R <sub>2</sub> | $1/R_1$       |

It can be observed that transfer functions in Table 2.1 only depend on the values R<sub>1</sub> and/or R<sub>2</sub> regardless of the source and load resistances. This is a desirable feature which closely approximates the performance of an ideal amplifier, since it reduces interaction between cascaded active circuits and improves control over the loop gain frequency response (module and phase). This feature greatly simplifies design from the system to circuit point of view (Palmisano et al., 1999).

At this point one may conclude that any of the four amplifiers might alternatively be used to implement the four types of feedback amplifiers. However, this is not the case if we consider non-ideal amplifiers with finite (albeit large) open lop gain, even with ideal internal resistances. In fact, under these assumptions, most of the 16 closed loop configurations, obtained by replacing the ideal amplifier with one of the four specified amplifiers (voltage op-amp, COA, OTA, OTRA), will exhibit a loop gain which is dependent on the source and/or load resistances (Palmisano et al., 1999).

Since the closed loop gain and bandwidth are strictly related to the loop gain, they will also depend on the source and/or load resistances. More specifically, this detrimental condition characterizes all the configurations in which the op-amp is a different type to the feedback amplifier (Palmisano et al., 1999).

To conclude, we can say that the best performance is obtained by following "natural laws" and that the use of voltage op-amp is not the prime choice in implementing current mode transfer functions. This perhaps represents the principal motivation that leads researchers to design more appropriate op-amp architectures which could be profitably used in current mode signal processing (Palmisano et al., 1999).

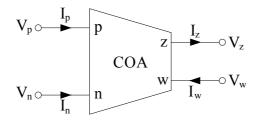

#### 2.5 Current Operational Amplifier

The circuit symbol of the COA is shown in Figure 2.8. The COA is a current-controlled current source whose defining equation can be given as

$$V_{p} = 0$$

$$V_{n} = 0$$

$$I_{z} = B(I_{p} - I_{n})$$

$$I_{w} = I_{z}$$

$$(2.1)$$

where *B* is the open loop current gain and ideally approaches infinity.

Figure 2.8 Circuit symbol of the COA

It seems to be the true current mode active element in current mode signal processing circuits. Both input terminals of COA are characterized by low impedance, thereby eliminating response limitations incurred by capacitive time constants. The input terminals are internally grounded leading to circuits that are insensitive to the stray capacitances. The output terminals of COA exhibit high impedance so that COA based current mode circuits can easily be cascaded without additional buffers. For ideal operation, the open loop current gain approaches infinity forcing the input currents to be equal in negative feedback configuration. Thus, the COA must be used in feedback configuration that is similar to the classical voltage op-amp. The use of high open loop gain of COA allows obtaining accurate transfer function. The current differencing and internally grounded inputs of COA make it possible to implement the COA based circuits with MOS-C realization.

As a wide range of voltage mode analog circuits already exist, a straight forward method of converting these voltage mode circuits to current mode circuits would be very useful. In such a method a circuit using voltage amplifiers and passive components is converted into one that contains current amplifiers and passive components. A voltage mode circuit can be converted into a current mode circuit by constructing an inter-reciprocal network by using the adjoint principle as described before (Koli, 2000).

Basically, the adjoint of a given network is found by replacing each element in that network by another according to the list given in Figure 2.4. As is apparent from Figure 2.4, the input voltage source is converted to a short circuit and the current through it now becomes the output response variable. Conversely, the output port voltage of the original network is excited by a current source. By the inter-reciprocal

property,  $V_{out}/V_{in} = I_{out}/I_{in}$ . Passive elements R and C in the adjoint network are the same as those in the original network. Lastly, a voltage amplifier with infinite input impedance and zero output impedance is transformed into a current amplifier with zero input impedance and infinite output impedance. This thereby provides the connection between well known voltage op-amp based active-RC circuits and COA based circuits (Roberts & Sedra, 1989). As an example, Figure 2.9 shows the current mode non-inverting amplifier which is obtained from the well known voltage op-amp based circuit.

Figure 2.9 Voltage and current mode non-inverting amplifiers

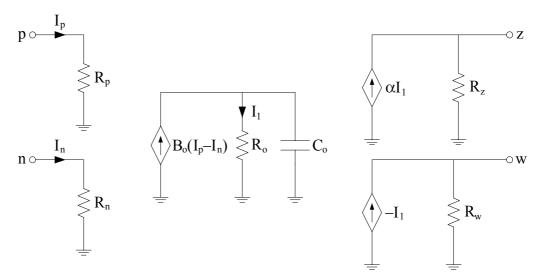

A simple model for the COA is shown in Figure 2.10. This model takes into consideration some basic non-idealities of the COA. Different from the ideal constitutive relation given in Equation (2.1), the voltages at the input terminals of a real COA are not exactly equal to zero. This non-ideal effect has been represented in the model of Figure 2.10 by two input resistance  $R_p$  and  $R_n$  which have small values. On the other hand, practically the open loop current gain, B, is finite and frequency dependent as oppose to the ideal case. The inner stage of the model represents this non-ideality. It contains a differential current-control current source, a resistor and a capacitor. For simplicity, a single-pole model is considered for the open loop current gain in Figure 2.10. The final stage stands for the non-ideal output resistances  $R_z$ ,  $R_w$ ; and also for the current tracking error between the two output terminals represented by  $\alpha$  which is very close to unity.

Figure 2.10 Simple COA model

#### 2.6 Operational Transresistance Amplifier

The circuit symbol of the OTRA is illustrated in Figure 2.11. OTRA is a high gain current input, voltage output device. The operation of the OTRA can be characterized by the following equations

$$\begin{split} V_p &= 0 \\ V_n &= 0 \\ V_z &= R_m (I_p - I_n) \end{split} \tag{2.2}$$

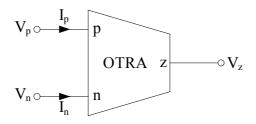

Figure 2.11 Circuit symbol of the OTRA

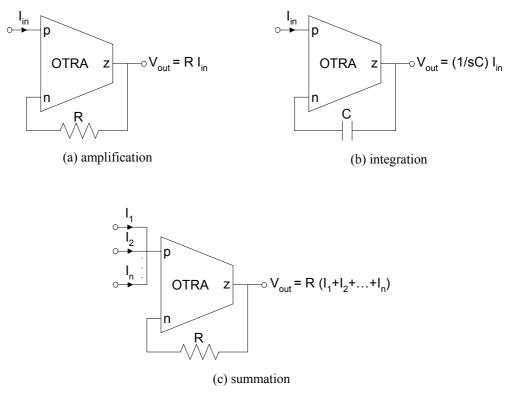

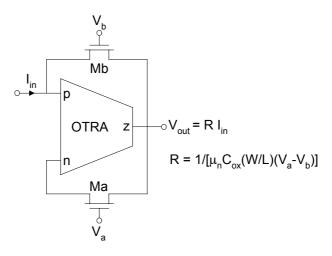

The OTRA, known also as current differencing amplifier or Norton amplifier, is an important active element in analog ICs and systems. Both input and output terminals of OTRA are characterized by low impedance, thereby eliminating response limitations incurred by capacitive time constants. Since the input terminals of OTRA are at ground potential, most effects of parasitic capacitances and resistances disappear. The output terminal of OTRA exhibits low impedance so that OTRA based voltage mode circuits can easily be cascaded without additional buffers. For ideal operation, the transresistance  $R_m$  approaches infinity forcing the input currents to be equal. Thus, the OTRA must be used in a feedback configuration in a way that is similar to the classical op-amp. It is possible to obtain very accurate and cascadable transfer functions by using this device in a negative feedback loop. Furthermore, it has been shown that the differential current input nature of this device considerably simplifies the implementation of MOS-C analog IC in contrast to their classical op-amp and unity gain active device counterparts.

Analog designers have been focusing their attention to the OTRA due to recent developments in current mode analog ICs (Chen et al., 1992; Chen, Tsao, Liu & Chiu, 1995; Salama & Soliman, 1999a; Salama & Soliman, 2000; Toumazou et al., 1990). Although the OTRA is commercially available from several manufacturers under the name of current differencing amplifier or Norton amplifier, it has not gained attention until recently. These commercial realizations do not provide internal ground at the input port and they allow the input current to flow in one direction only. The former disadvantage limits the functionality of the OTRA whereas the latter forces to use external DC bias current leading complex and unattractive designs (Salama & Soliman, 1999a; Salama & Soliman, 2000). In recent years, several high performance CMOS OTRA realizations have been presented in the literature (Chen et al., 1992; Salama & Soliman, 1999a). This leads to growing interest for the design of OTRA based analog signal processing circuits. On the other hand, OTRA is similar building block to the CDBA (Acar & Özoğuz, 1999). It can also be implemented by CDBA with its output current terminal open circuited.

OTRA has the advantages of high slew rate and wide bandwidth due to the fact that it benefits from the current processing capabilities at the input terminals. On the other hand, since its output terminal is characterized as low impedance, OTRA is suitable for voltage mode operations keeping the compatibility with existing signal processing circuits (Salama & Soliman, 1999a).

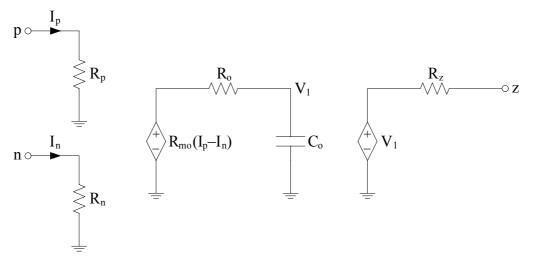

Figure 2.12 Simple OTRA model

A simple model for the OTRA is shown in Figure 2.12. The input stage is same as that of the COA model. The inner stage is again for representing the finite and frequency dependent open loop transresistance gain,  $R_{\rm m}$ . It comprises series combination of differential current-control voltage source, a resistor and a capacitor in which a single-pole model for  $R_{\rm m}$  is used. The final stage stands for the non-ideal series output resistance  $R_z$ .

## CHAPTER THREE CMOS REALIZATION EXAMPLES FOR COA

#### 3.1 Block Diagram Model of the COA

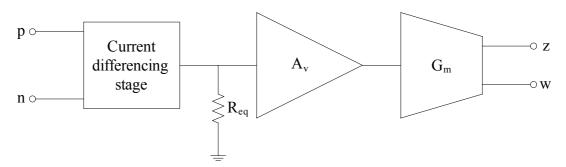

The ideal COA has been introduced before and recognized that, according to adjoint networks theorem, it can be represented as the dual of an ideal op-amp. The theorem can also be exploited to obtain one possible COA internal architecture from that of a voltage op-amp (Palmisano et al., 1999). The block diagram model of the COA which is obtained by applying the adjoint theorem to the well known internal architecture of the voltage op-amp is shown in Figure 3.1.

Figure 3.1 Internal architecture of the COA

The input stage of this model serves as a current buffer and also subtracts the currents flowing into the two input terminals of the COA. The input impedances of this stage are very low, ideally zero, whereas the output impedance is high. The difference of input currents at the output of the first stage flows into this high impedance and converted to a voltage signal. Therefore, we have voltage signal information that is proportional to the difference of the input currents at the input of the second stage. Since we need a very high, ideally infinite, open loop current gain for the COA, this signal is further amplified by the inner stage, which is basically a high gain voltage amplifier. To convert this amplified voltage information into two balanced currents, we need a dual output transconductance amplifier as the final stage. Block diagram of the COA is obtained by this manner as shown in Figure 3.1. For this model, the open loop current gain can be expressed as  $B=R_{eq}A_vG_m$ .

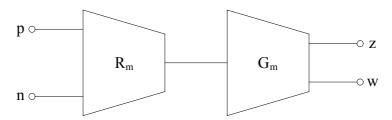

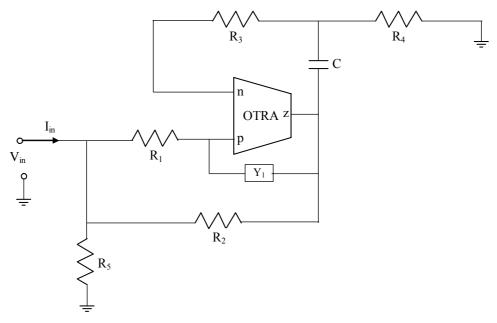

In the block model of Figure 3.1, the second stage, which is used to increase gain, might sometimes not be necessary for the implementation of the COA if the impedance of the internal node is high enough. Therefore, the input current differencing stage together with the second stage can be regarded as a transresistance amplifier. With this approach, the COA can be implemented using a transresistance input stage (or OTRA) followed by a transconductance output stage (or dual output OTA) as shown in Figure 3.2.

Figure 3.2 Block diagram of two-stage COA

The first stage is a high gain transresistance amplifier to convert the two input currents into voltage, followed by a high gain transconductance amplifier to convert the voltage into two balanced currents. The transresistance amplifier is responsible for providing the low input impedance of the COA, while the transconductance amplifier is responsible for providing the high output impedance of the COA. A compensating capacitor can be inserted at the high impedance node between these two stages. For this block diagram, the open loop current gain can be expressed as  $B=R_mG_m$ .

#### 3.2 Implementation of COA Using Current Conveyors

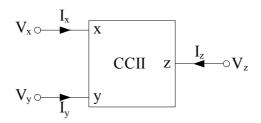

The block diagram representation of COA internal architecture can be implemented by using the combinations of the other well known active elements. From a high level point of view, current amplifiers can usefully be described by a basic current mode block, the second generation current conveyor. Defining equations of the second generation current conveyor, circuit symbol of which is shown in Figure 3.3, can be given as

$$I_{y} = 0$$

$$V_{x} = V_{y}$$

$$I_{z} = \pm I_{x}$$

(3.1)

where + sign in the last equation is for positive type current conveyor, whereas – sign is for negative type current conveyor.

Figure 3.3 Circuit symbol of current conveyor

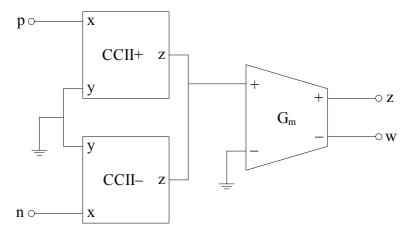

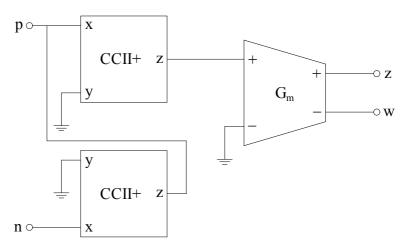

The block diagram of COA based on current conveyors and dual output OTA is shown in Figure 3.4. It employs one positive and one negative type current conveyor as the input stage. This combination is for subtracting the input currents and also for achieving low input resistances. The difference of the input currents is converted to voltage at the internal high impedance node. This voltage is then transformed to two balanced output currents by the dual output transconductance amplifier.

Figure 3.4 COA implementation with current conveyors and OTA

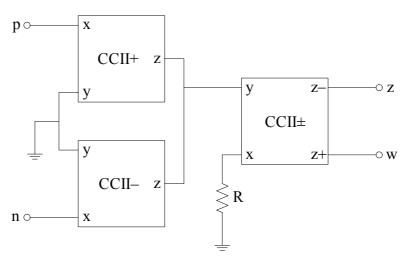

The output transconductance stage in Figure 3.4 can also be implemented using a dual output current conveyor. The resulting block diagram that uses only second generation current conveyors is shown in Figure 3.5.

Figure 3.5 Block diagram of current conveyor based COA

The realization of Figure 3.5 consists of two input second generation current conveyors, one of which is positive type and the other is negative type. The two input currents are applied to the X terminals of the input current conveyors as shown in Figure 3.5. The Z terminal currents of both current conveyors are added at the Y terminal of the third dual output current conveyor, which is a high impedance node. This corresponds to subtracting the two input currents and multiplying them by the output impedance of the two input current conveyors connected in parallel. The voltage generated at the Y terminal is copied to the X terminal of the dual output current conveyor, where it is converted to a current using the resistor R. This current is then conveyed to the two balanced output terminals. It can be shown that at low frequencies the open loop current gain can be given as  $B=R_{out}/R$  where  $R_{out}$  is the output resistance of the input current conveyors connected in parallel (Youssef & Soliman, 2005).

There are some disadvantages of this architecture. Firstly, to maximize the gain, *R* should be shorted to ground or chosen a very small value, but the voltage following property between the X and Y terminals of the current conveyor is not insured in this

case. Secondly, the output resistance of the input current conveyors is reduced due to their parallel connection. Finally, matching the two current conveyor blocks is not an easy design task due to their different polarities (Youssef & Soliman, 2005).

For taking the difference of two input currents another current conveyor based implementation, this time both of which are positive type, is also possible as shown in Figure 3.6.

Figure 3.6 Another COA implementation

In the block diagram of the COA shown in Figure 3.6, the two input currents are sensed using two positive type second generation current conveyors to provide very low input resistance, and low offset voltage. The two currents are subtracted at one of the input nodes and the corresponding current conveyor conveys the current difference to the Z terminal. The current difference is multiplied by the high output resistance of the current conveyor to generate a voltage. This voltage is applied to a transconductor with two balanced output currents (Youssef & Soliman, 2005).

This architecture has some advantages. Firstly, both currents are subtracted at the input of the first current conveyor and not at the high impedance node, thus the gain is enhanced. Secondly, the output current conveyor in Figure 3.5 is removed and replaced by a balanced output transconductor. Finally, it is easier to match between the two current conveyors as they have the same polarity. The open loop current gain of the COA can be expressed as  $B=R_{out}G_m$  where  $R_{out}$  is the output resistance of the

current conveyor. From the above equation, it is evident that the block diagram in Figure 3.6 leads to the same gain when cascading a transresistance and transconductance amplifiers, but in this case simple current conveyors replace the transresistance amplifier (Youssef&Soliman, 2005).

## 3.3 The First Example of CMOS COA Realization

With the aid of the block diagram representations for COA internal architecture given in the previous sections, many CMOS COA realizations have been presented before (Abou-Allam & El-Masry, 1997; Awad & Soliman, 2000; Bruun, 1991; Kaulberg, 1993; Mucha, 1995; Palmisano et al., 1999). However, most of these implementations do not satisfy the desirable property of differential input balanced output. In the present and following sections, we introduce two fully differential CMOS COA realizations.

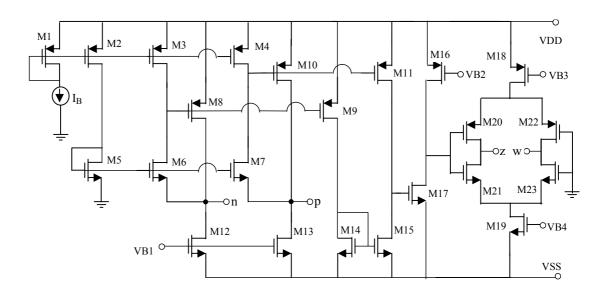

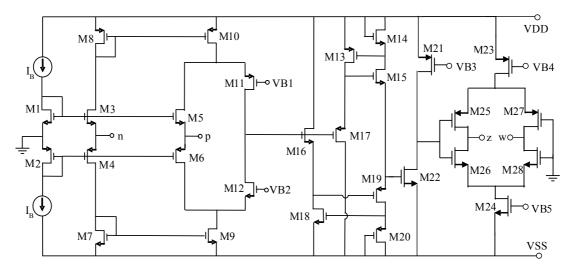

Figure 3.7 The first example circuit of dual output CMOS COA

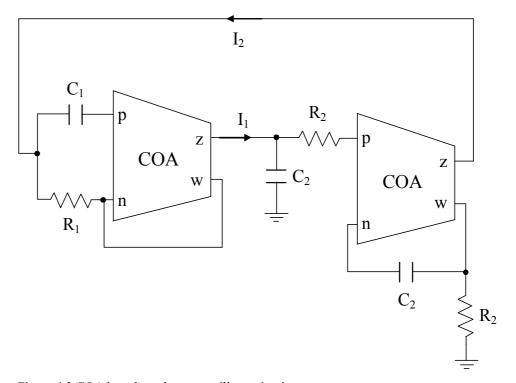

The circuit schematic of the first CMOS COA example is shown in Figure 3.7. It consists of cascade connected modified differential current conveyor (Elwan & Soliman, 1996), a common source amplifier (Salama & Soliman, 1999a) and a floating current source. While transistors M1-M15 perform a current differencing operation (Nagasaku, Hyogo & Sekine, 1996; Tangsritat, Surakampontorn & Fujii,

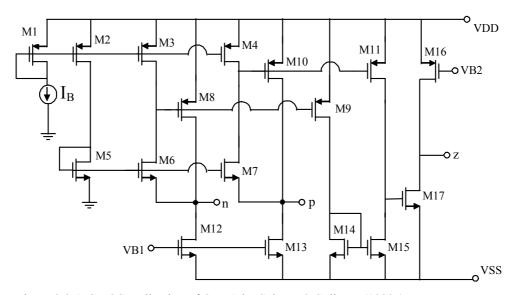

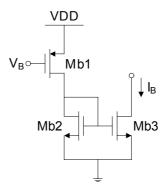

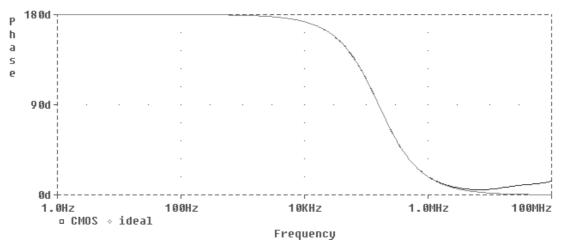

2003), the common source amplifier that consists of transistors M16-M17 provides the high gain stage. This voltage is then converted into two balanced output currents by the floating current source formed by transistors M18-M23, which requires no transistor matching constraint unlike current mirror structures. Essentially, this stage is just two matched CMOS inverters biased by two current sources and operates as an analog transconductor stage (Arbel & Goldminz, 1992). The first two stage of the circuit in Figure 3.7, i.e., the part comprising transistors M1 through M17, actually constitutes a CMOS realization of OTRA (Salama & Soliman, 1999a), which is given in Figure 3.8. The bias current I<sub>B</sub> in Figures 3.7 and 3.8 can be realized as shown in Figure 3.9.

Figure 3.8 A CMOS realization of OTRA by Salama & Soliman (1999a)

Figure 3.9 Biasing circuit

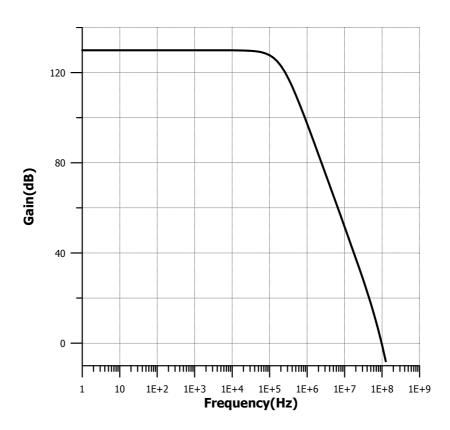

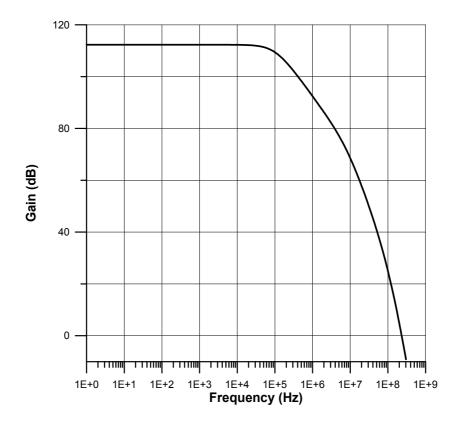

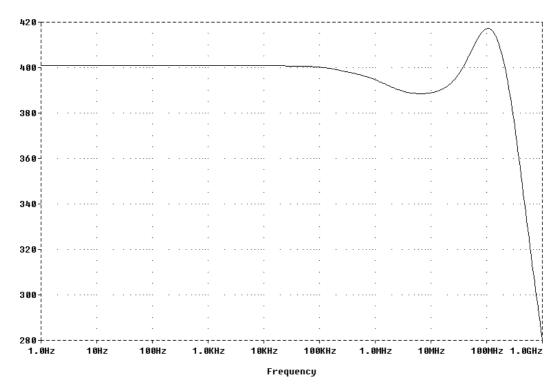

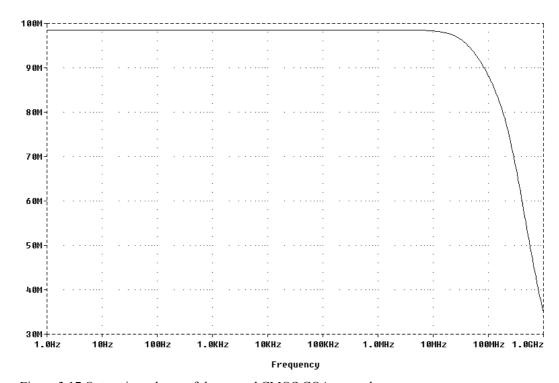

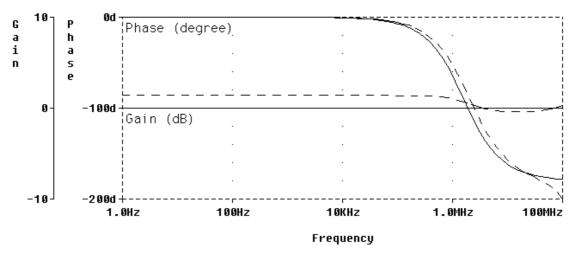

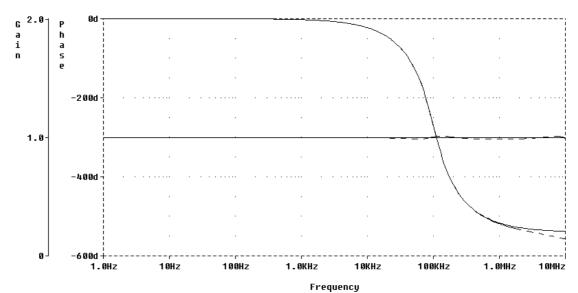

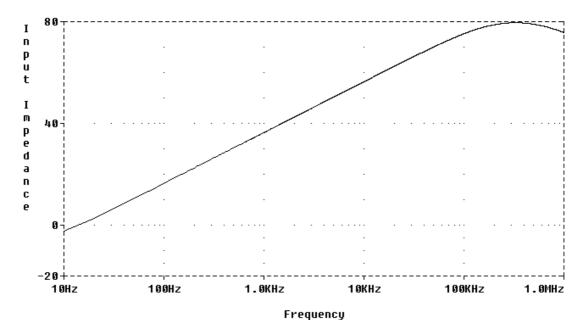

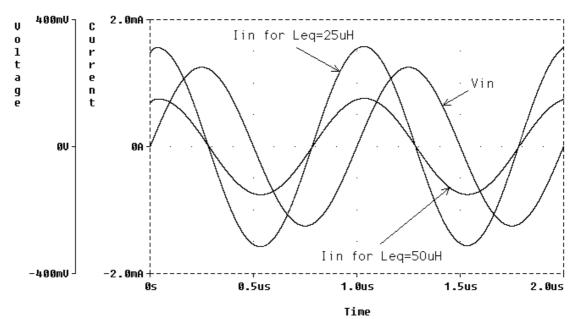

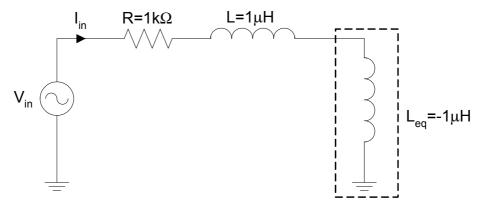

The presented CMOS COA circuit has been simulated using PSPICE program on the basis of AMI 1.2 $\mu$ m CMOS process parameters. MOS transistor aspect ratios are taken as follows: M1-M17: 30/3, M18-M19: 300/3, M20-M23: 100/3. Supply voltages are taken as  $V_{DD}$ =2.5V and  $V_{SS}$ =-2.5V and the bias voltages are  $V_{B1}$ =-0.3V,  $V_{B2}$ =0.3V,  $V_{B3}$ =1.3V,  $V_{B4}$ =-1.6V. Open loop current gain of the circuit is given in Figure 3.10, which shows that the cut-off frequency is nearly 150kHz whereas the unity gain bandwidth is close to 100MHz. The open loop gain of the first CMOS COA example is 130dB and phase margin is 55°. Simulated input and output impedances are depicted in Figures 3.11 and 3.12 respectively.

Figure 3.10 Simulated open loop gain of the first CMOS COA example

The first CMOS COA example provides high performance in terms of frequency response and open loop gain compared to most of the CMOS COAs in the literature (Abou-Allam & El-Masry, 1997; Awad & Soliman, 2000; Bruun, 1991; Kaulberg, 1993; Mucha, 1995; Palmisano et al., 1999). Some numerical performance parameters of the first CMOS COA example is given in Table 3.1.

Figure 3.11 Input impedance of the first CMOS COA example

Figure 3.12 Output impedance of the first CMOS COA example

| Table 3.1 Some numerical | performance ' | parameters of the | first CMO | S COA example |

|--------------------------|---------------|-------------------|-----------|---------------|

|                          |               |                   |           |               |

| Open loop current gain | 130 dB                 |

|------------------------|------------------------|

| Unity gain bandwidth   | 100 MHz                |

| Cut-off frequency      | 150 kHz                |

| Phase margin           | 55°                    |

| Slew rate              | $15 \mu A/ns$          |

| Input resistances      | $5~\Omega$             |

| Output resistances     | $100~\mathrm{M}\Omega$ |

## 3.4 The Second Example of CMOS COA Realization

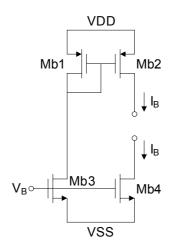

The second example of CMOS COA realization is shown in Figure 3.13. It is constructed by cascading an OTRA, a voltage amplifier and a dual output OTA. The first stage, composed of transistors M1 through M20, was originally proposed for the realization of CDBA (Toker, Özoğuz, Çiçekoğlu & Acar, 2000). It can also be used as the OTRA with open circuited z terminal of CDBA. It consists of a differential current controlled current source followed by a voltage buffer. The second stage (M21-M22), which is a common source amplifier, provides extra gain. The final stage is the floating current source (Arbel & Goldminz, 1992) formed by transistors M23-M28 and operates as an analog transconductor. The bias currents I<sub>B</sub> in Figure 3.13 can be realized as shown in Figure 3.14.

Figure 3.13 The second example circuit of dual output CMOS COA

Figure 3.14 Biasing circuit

Table 3.2 Transistor aspect ratios for the second CMOS COA example in Figure 3.10

| Transistor | W (µm) | L (µm) | Transistor | W (µm) | L (µm) |

|------------|--------|--------|------------|--------|--------|

| M1         | 40     | 1      | M15        | 200    | 1      |

| M2         | 160    | 1      | M16        | 200    | 1      |

| M3         | 40     | 1      | M17        | 400    | 1      |

| M4         | 160    | 1      | M18        | 200    | 1      |

| M5         | 40     | 1      | M19        | 300    | 1      |

| M6         | 160    | 1      | M20        | 400    | 1      |

| M7         | 10     | 2.5    | M21        | 400    | 1      |

| M8         | 40     | 2.5    | M22        | 400    | 1      |

| M9         | 10     | 2.5    | M23        | 300    | 1      |

| M10        | 40     | 2.5    | M24        | 300    | 1      |

| M11        | 16     | 1      | M25        | 50     | 1      |

| M12        | 4      | 1      | M26        | 50     | 1      |

| M13        | 400    | 1      | M27        | 50     | 1      |

| M14        | 150    | 1      | M28        | 50     | 1      |

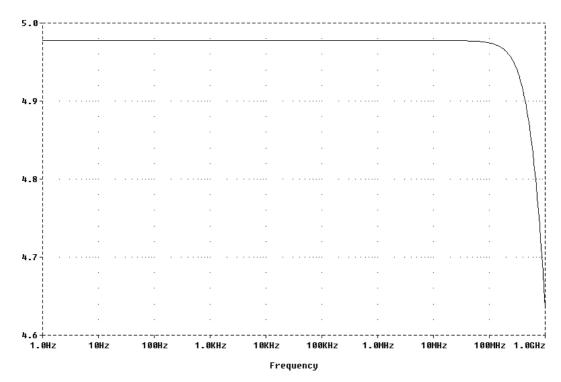

The presented CMOS COA circuit has been simulated using PSPICE program on the basis of MIETEC 0.5 $\mu$ m CMOS process parameters. MOS transistor aspect ratios are given in Table 3.2. Supply voltages are taken as  $V_{DD}$ =2.5V and  $V_{SS}$ =-2.5V and the bias voltages are  $V_{B1}$ =-1.05V,  $V_{B2}$ =0.1V,  $V_{B3}$ =-1.071V,  $V_{B4}$ =1V,  $V_{B5}$ =-1V. Open loop current gain of the circuit is given in Figure 3.15, which shows that the

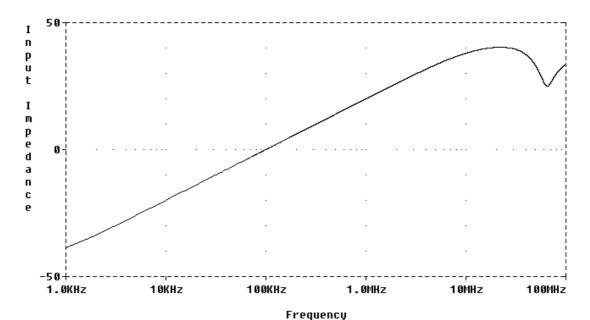

cut-off frequency is nearly 200kHz whereas the unity gain bandwidth is close to 230MHz. The open loop gain of the second CMOS COA example is 110dB and phase margin is 45°. Simulated input and output impedances are depicted in Figures 3.16 and 3.17 respectively. Some numerical performance parameters of the second CMOS COA example is given in Table 3.3.

Figure 3.15 Simulated open loop gain of the second CMOS COA example

Table 3.3 Some numerical performance parameters of the second CMOS COA example

| Open loop current gain | 110 dB                 |

|------------------------|------------------------|

| Unity gain bandwidth   | 230 MHz                |

| Cut-off frequency      | 200 kHz                |

| Phase margin           | 45°                    |

| Slew rate              | $20~\mu\text{A/ns}$    |

| Input resistances      | $400~\Omega$           |

| Output resistances     | $100~\mathrm{M}\Omega$ |

Figure 3.16 Input impedance of the second CMOS COA example

Figure 3.17 Output impedance of the second CMOS COA example

# CHAPTER FOUR ANALOG CIRCUIT DESIGN USING COA

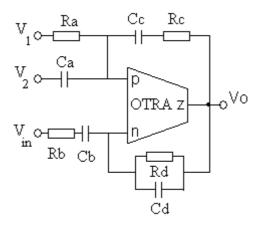

In this Chapter, we present some new circuits as the applications of the CMOS COA realizations introduced in Chapter 3. We start with a first order allpass filter, which includes a bare minimum number of passive components. Then a biquadratic filter configuration is presented. Second order lowpass, highpass, bandpass, and notch filters can be realized using this configuration. Finally, a sinusoidal oscillator configuration, which allows obtaining ten different oscillators, is presented.

All of these filter and oscillator circuits employ only one COA as the active element. This feature is advantageous in terms of power consumption. They also enjoy the properties of the COA presented in Chapter 2. The proposed filters and oscillators have high output impedances since the output current is taken from one of the output terminals of the COA that is characterized as high impedance. This property enables the filters to be cascaded without the addition of a buffer. Also, the high output impedance of the oscillators allows for driving the loads without the addition of a buffer. On the other hand, the circuits are insensitive to parasitic input capacitances and input resistances due to internally grounded input terminals of COA.

#### 4.1 Current Mode First Order Allpass Filters

Allpass filters are one of the most commonly used filter types of all. They are generally used for introducing a frequency dependent delay while keeping the amplitude of the input signal constant over the desired frequency range. Other types of active circuits such as oscillators and high Q bandpass filters are also realized by using allpass filters (D. J. Comer & McDermid, 1968; D. T. Comer, D. J. Comer & Gonzalez, 1997; Moschytz, 1972; Schauman & Van Valkenburg, 2001; Tarmy & Ghausi, 1970). Current mode filters reported in literature, either do not offer allpass configurations at all, or are excess in the number of components and require component matching constraints (Çam, Çiçekoğlu, Gülsoy & Kuntman, 2000;

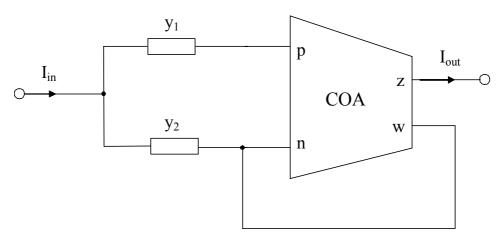

Chang, 1991a; Higashimura, 1991; Higashimura & Fukiu, 1988; Liu & Hwang, 1997). Recently, a CDBA based first order current mode allpass filter configuration is proposed (Toker et al., 2000). The circuit uses single CDBA, a resistor and a capacitor, which are of minimum number. However, the transfer function of the circuit is sensitive to current tracking error of the CDBA and the accuracy of CMOS CDBA depends on matching of MOS transistors. It is a well known fact that open loop circuits are less accurate compared to their high gain counterparts. On the other hand, COA is a high gain current-input, current-output device. Using this device in negative feedback configuration makes it possible to obtain very accurate transfer functions (Awad & Soliman, 2000; Mucha, 1995). In this section, COA based current mode first order allpass filter configuration is presented (Kılınç & Çam, 2003a, 2003b, 2004a). The circuit uses single COA, a resistor and a capacitor, which are of minimum number. A sinusoidal quadrature oscillator is implemented to show the usefulness of the filter configuration as an illustrating example.

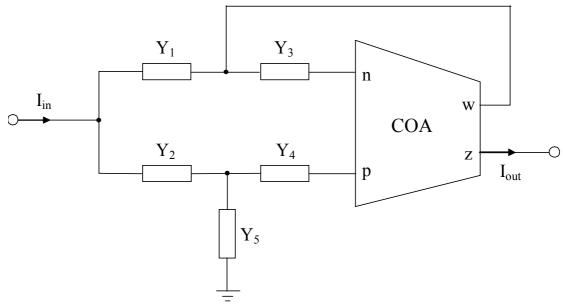

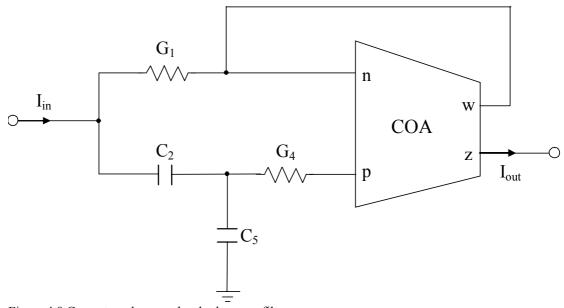

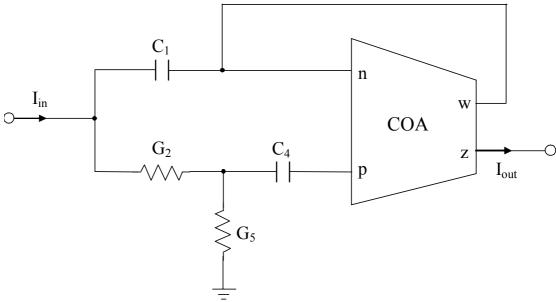

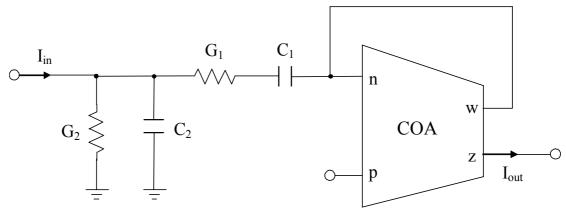

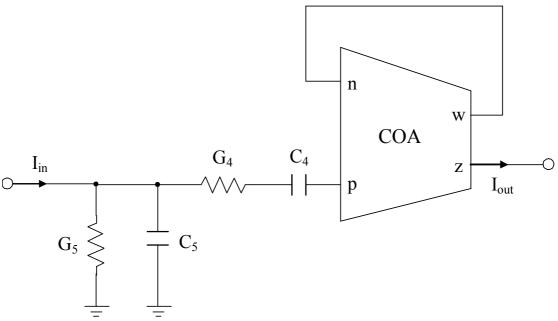

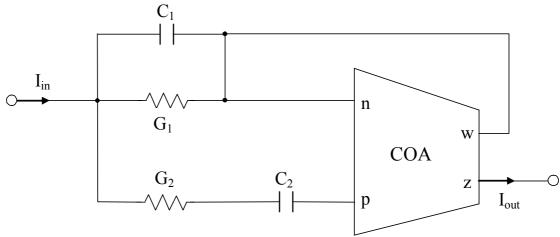

Figure 4.1 Current mode first order allpass filter configuration

The current mode first order allpass filter configuration is shown in Figure 4.1. Routine analysis yields the current transfer function as follows

$$T(s) = \frac{I_{out}}{I_{in}} = \frac{y_2 - y_1}{y_2 + y_1}$$

(4.1)

This transfer function allows to designer two different types of realizations for first order allpass filter by choosing  $y_1$  and  $y_2$  appropriately.

For  $y_1 = G$  and  $y_2 = sC$  the transfer function becomes

$$T_1(s) = \frac{I_{out}}{I_{in}} = \frac{sC - G}{sC + G}$$

(4.2)

For  $y_1 = sC$  and  $y_2 = G$  the transfer function becomes

$$T_2(s) = \frac{I_{out}}{I_{in}} = -\frac{sC - G}{sC + G}$$

(4.3)

Thus, both inverting and noninverting types of first order current mode allpass filters are realized using only a single COA, a resistor and a capacitor without imposing any passive element matching condition. The outputs of the filters exhibit high impedance so that the synthesized current mode filters can be cascaded without additional buffers. Most of the effects of parasitic input impedances disappear for the presented allpass filters due to internally grounded input terminals of COA. The allpass filters have the following phase responses

$$\varphi_{1}(\omega) = 180^{\circ} - 2 \arctan\left(\frac{\omega C}{G}\right)$$

$$\varphi_{2}(\omega) = -2 \arctan\left(\frac{\omega C}{G}\right)$$

(4.4)

As it can be seen from the defining equation of the COA given in Chapter 2, there are two main non-ideal effects. The first one is the current tracking error between z and w terminals which can be represented by  $\alpha(I_z = \alpha I_w)$ . The other non-ideality is nonzero voltage at p and n terminals. This can be considered by connecting parasitic admittances  $y_p$  and  $y_n$  between the ground and p and n terminals, respectively. Routine analysis yields modified transfer function to be as follows

$$T(s) = \frac{I_{out}}{I_{in}} = \frac{1}{\alpha} \frac{y_1 y_n y_p - y_2 y_n y_p + y_1 y_2 (y_p - y_n)}{y_1 y_n y_p + y_2 y_n y_p + y_1 y_2 (y_n - y_p)}$$

(4.5)

It is apparent from Equation (4.5) that current tracking error does not affect center frequency. We can also eliminate the effects of parasitic input resistances and capacitances by a careful circuit realization of COA that provides  $y_p = y_n$ .

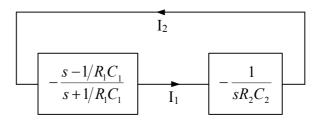

Figure 4.2 Block diagram for quadrature oscillator

Figure 4.3 COA based quadrature oscillator circuit

It is a well known fact that a sinusoidal quadrature oscillator can be realized using an allpass section and an integrator (Haritantis, 1985) as shown in Figure 4.2. Using this block diagram, COA based current mode quadrature oscillator can be implemented as shown in Figure 4.3. In this circuit, the presented allpass filter and a

current mode integrator employing a COA with two matched resistors and capacitors are used. For providing a sinusoidal oscillation the loop gain of the circuit is set to unity at  $s = j\omega$ , i.e.

$$\left[ -\frac{s - 1/R_1 C_1}{s + 1/R_1 C_1} \right] \left[ -\frac{1}{sR_2 C_2} \right]_{s = i\omega} = 1$$

(4.6)

From Equation (4.6) oscillation condition and frequency can be found respectively as

$$R_1 C_1 = R_2 C_2 \tag{4.7}$$

$$\omega_0 = \sqrt{\frac{1}{R_1 C_1 R_2 C_2}} \tag{4.8}$$

For simplicity, if we choose  $R_1 = R_2 = R$  and  $C_1 = C_2 = C$ , oscillation condition is satisfied and oscillation frequency becomes

$$\omega_0 = \frac{1}{RC} \tag{4.9}$$

The sensitivity analysis of this oscillator shows that

$$S_{R_1}^{\omega_0} = S_{R_2}^{\omega_0} = S_{C_1}^{\omega_0} = S_{C_2}^{\omega_0} = -1/2$$

which are all less than unity in magnitude.

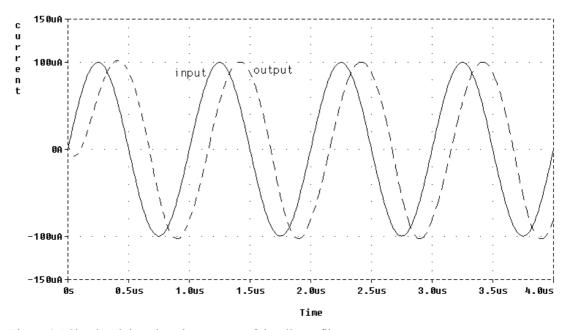

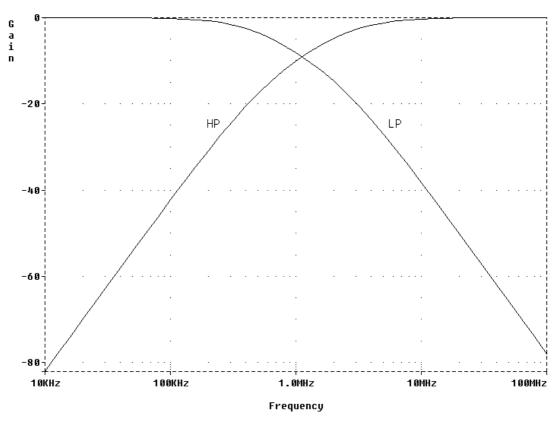

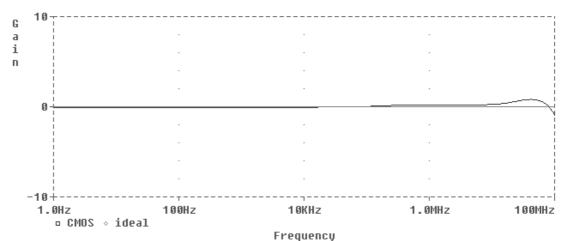

To verify the theoretical study, the first order allpass filter was constructed and simulated using PSPICE program on the basis of AMI 1.2 $\mu$ m CMOS process parameters. For this purpose, passive components were chosen as R=10k $\Omega$  and C=10pF, which results in a 1.59MHz center frequency. The PSPICE simulations were performed using the CMOS realization of the COA given in Figure 3.7. The supply voltages were taken as  $V_{DD}$ =2.5V and  $V_{SS}$ =-2.5V. Simulation results of the filter response with ideal and CMOS COA are given in Figure 4.4, which are in good agreement with the predicted theory. Figure 4.5 shows the time domain response of the filter. A sinusoidal input at a frequency of 1MHz was applied to the allpass network constructed with above mentioned passive element values. This causes a

176ns time delay at the output of the filter corresponding to a 63° phase difference which is very close to the theoretical value (64°).

Figure 4.4 Simulation result of the allpass filter; ——— ideal COA, ----- CMOS COA

Figure 4.5 Simulated time domain response of the allpass filter

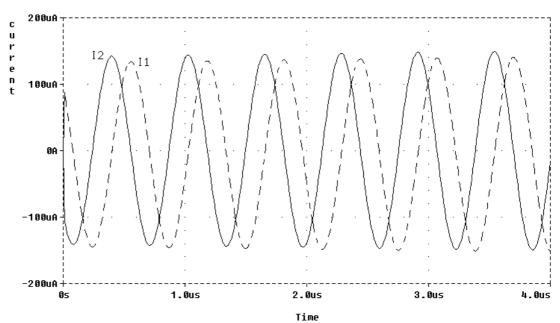

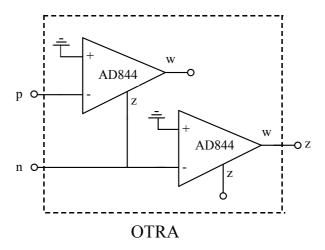

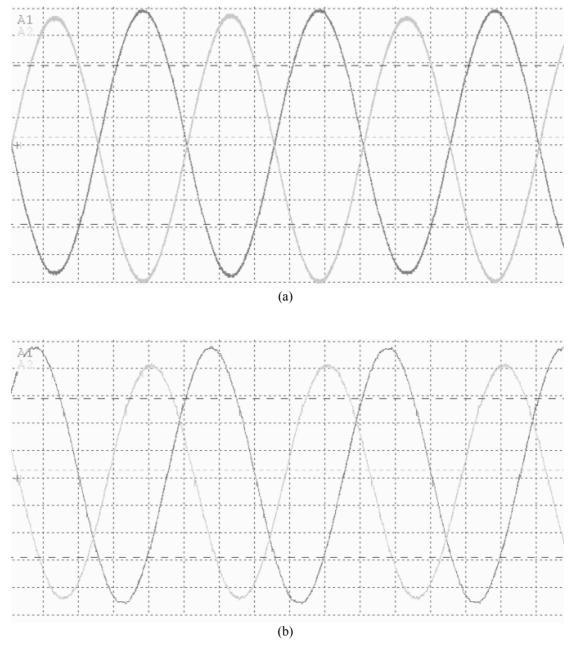

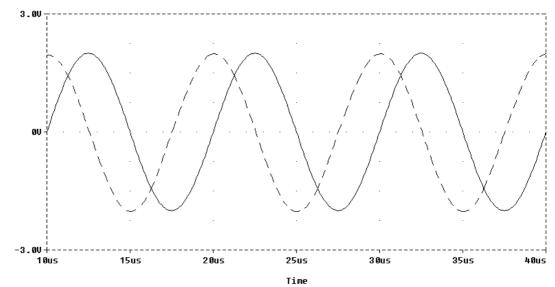

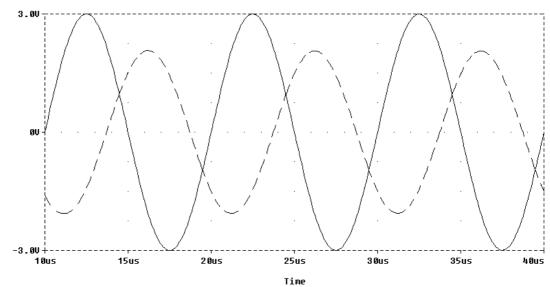

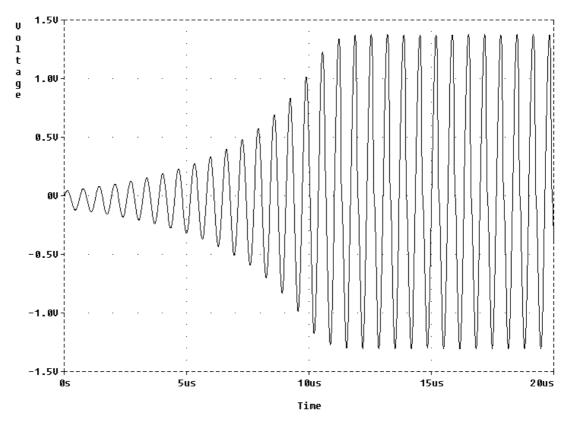

Quadrature oscillator employing the presented allpass filter has also been simulated using PSPICE. In this simulation, all resistances and capacitances were taken as  $10k\Omega$  and 10pF respectively which results in a 1.59MHz oscillation frequency. The output waveforms of the oscillator are shown in Figure 4.6.

Figure 4.6 Simulated output waveforms of the quadrature oscillator

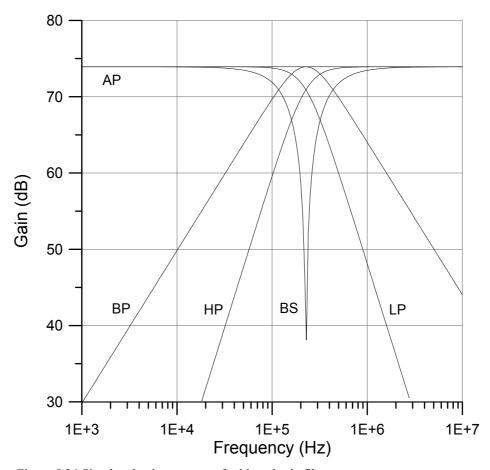

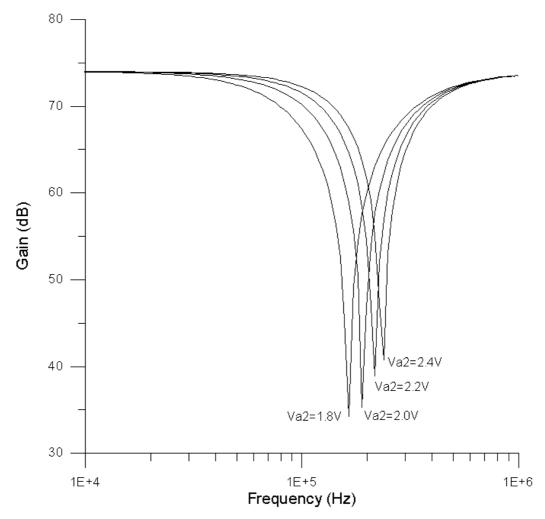

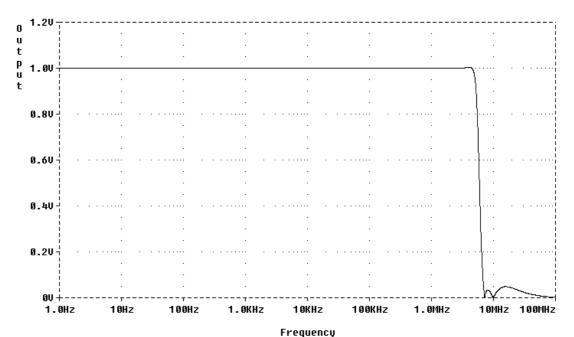

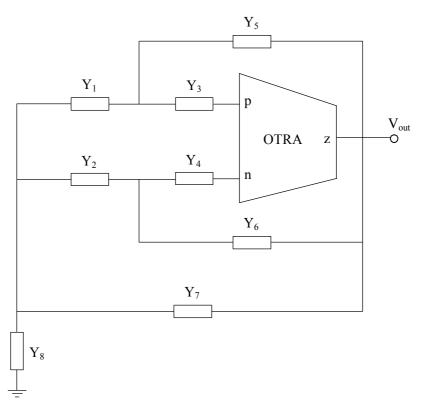

#### 4.2 Current Mode Biquadratic Filters