# DOKUZ EYLÜL UNIVERSITY GRADUATE SCHOOL OF NATURAL AND APPLIED SCIENCES

# FACE AND FINGERPRINT RECOGNITION ON FIELD PROGRAMMABLE GATE ARRAY

by Enes DİLCAN

October, 2010 İZMİR

# FACE AND FINGERPRINT RECOGNITION ON FIELD PROGRAMMABLE GATE ARRAY

A Thesis Submitted to the

Graduate School of Natural and Applied Sciences of Dokuz Eylül University In Partial Fulfillment of the Requirements for the Degree of Master of Science in Electrical and Electronics Engineering

> by Enes DİLCAN

October, 2010 IZMIR

### M.Sc THESIS EXAMINATION RESULT FORM

We have read the thesis entitled **"FACE AND FINGERPRINT RECOGNITION ON FIELD PROGRAMMABLE GATE ARRAY"** completed by **ENES DİLCAN** under supervision of **ASST. PROF. DR. NALAN ERDAŞ ÖZKURT** and we certify that in our opinion it is fully adequate, in scope and in quality, as a thesis for the degree of Master of Science.

Asst. Prof. Dr. Nalan Erdaş ÖZKURT

Supervisor

(Jury Member)

.....

(Jury Member)

Prof.Dr. Mustafa SABUNCU Director Graduate School of Natural and Applied Sciences

### ACKNOWLEDGEMENTS

I would like to thank my advisor Asst. Prof. Dr. Nalan Erdaş ÖZKURT for her guidance and support in every stage of my research. The technique background and the research experience I have gained under her care will be valuable asset to me in the future.

I also would like to thank to my dear friend Gökhan ÇETİN for his absolute guidance, supports and patience during this research. His endless friendship and encouragement always motivated me.

Finally, I would like to thank Çiğdem COŞKUN and my family for their motivation and never ending support throughout my life.

Enes DİLCAN

### FACE AND FINGERPRINT RECOGNITION ON FIELD PROGRAMMABLE GATE ARRAY

#### ABSTRACT

Biometric recognition refers to use of distinctive physiological and behavioral characteristics for automatically recognizing a person. A number of biometric technologies have been developed such as fingerprint, face, iris and speech are the ones that most commonly used. Feature extraction techniques play important role for biometric recognition system design.

Field Programmable Gate Arrays (FPGAs) are the programmable logic devices that can be configured by the customer after manufacturing. FPGAs are preffered in a variety of applications due to ease of programming with low cost. Applications of FPGAs include digital signal processing, biometric recognition, medical imaging aerospace and defense systems, computer vision and a growing range of other areas.

In this thesis, face and fingerprint recognition systems are implemented on FPGA. This study has two working phases. In the offline training phase, face and fingerprint images are collected by MATLAB. Then, this database is sent to FPGA to extract features. Principal Component Analysis (PCA) is the feature extraction algorithm that is used in this study. After all features of face and fingerprint images are extracted, the features are stored on the memory of FPGA. In the online test phase or recognition phase, the features of test images are extracted then these are compared to restored values of the database from the memory of FPGA. The result of comparison is then displayed. This thesis also proposes a multibiometric recognition systems which is constituted from face and fingerprint recognition systems by using the fusion at the decision level.

**Keywords :** Face recognition, fingerprint recognition, multibiometric recognition, FPGA, PCA

### SAHADA PROGRAMLANABİLİR KAPI DİZİLERİ ÜZERİNDE YÜZ VE PARMAK İZİ TANIMA

### ÖΖ

Biyometrik tanıma, otomatik olarak bir kişiyi ayırıcı fiziksel ve davranışsal niteliklerine göre tanımaya karşılık gelir. Çok sayıda biyometrik teknoloji geliştirilmiştir. Parmak izi, yüz, iris ve ses tanıma en yaygın kullanılan biyometrik teknolojilerdir. Özellik çıkarma metotları, biyometrik sistem tasarımında önemli bir rol oynamaktadır.

Sahada Programlanabilir Kapı Dizileri (SPKD), üretimden sonra müşteri tarafından yeniden yapılandırılabilen programlanabilir mantık elemanlarıdır. SPKD'ler düşük maliyetle ve programlanabilme kolaylığı ile çok sayıda uygulamada tercih edilmektedir. SPKD içeren uygulamalar sayısal işaret işleme, biyometrik tanıma, medikal görüntü işleme, uzay ve savunma sistemleri, bilgisayar görüntüsü alanlarında kullanmakta ve kullanım alanları giderek artmaktadır.

Bu tezde, SPKD üzerinde yüz ve parmak izi tanıma sistemi gerçeklenmiştir. Bu sistemin iki çalışma aşaması vardır. Çevrimdışı öğrenme aşamasında, yüz ve parmak izi resimleri MATLAB tarafından toplanır. Daha sonra oluşturulan bu veritabanı öznitelik çıkarma için SPKD'ye gönderilir. Bu çalışmada öznitelik çıkarmak için Temel Bileşen Analizi (TBA) algorithması kullanılmıştır. Yüz ve parmak izindeki tüm öznitelikler çıkarıldıktan sonra, bu öznitelikler SPKD'nin hafizasında saklanır. Çevrimiçi deneme ya da tanıma aşamasında, öncelikle yüz ve parmak izi resimlerinden öznitelikler çıkarılır, daha sonra bu öznitelikler SPKD'nin hafizasında saklanan veritabanı ile karşılaştırılır. Karşılaştırma sonucu, tanımlama sonucudur. Bu tezde ayrıca yüz ve parmak izi tanıma sistemlerininden oluşan, birleştirmenin karar verme seviyesinde yapıldığı çoklu biyometrik tanıma sistemi tasarlanmıştır.

Anahtar Sözcükler : Yüz tanıma, parmak izi tanıma, çoklu biyometrik tanıma, Sahada Programlanabilir Kapı Dizileri, Temel Bileşen Analizi

### CONTENTS

## Page

| M.Sc THESIS EXAMINATION RESULT FORMii                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ACKNOWLEDGEMENTSiii                                                                                                                                                                                                                                                                                    |

| ABSTRACTiv                                                                                                                                                                                                                                                                                             |

| ÖZ v                                                                                                                                                                                                                                                                                                   |

|                                                                                                                                                                                                                                                                                                        |

| CHAPTER ONE – INTRODUCTION 1                                                                                                                                                                                                                                                                           |

| 1.1 Biometric Systems                                                                                                                                                                                                                                                                                  |

| 1.2 Multibiometric Systems                                                                                                                                                                                                                                                                             |

| 1.3 History of Face Recognition Systems                                                                                                                                                                                                                                                                |

| 1.4 History of Fingerprinting7                                                                                                                                                                                                                                                                         |

| 1.5 Aim of Thesis                                                                                                                                                                                                                                                                                      |

| 1.6 Outline of Thesis 11                                                                                                                                                                                                                                                                               |

|                                                                                                                                                                                                                                                                                                        |

|                                                                                                                                                                                                                                                                                                        |

| CHAPTER TWO – FACE RECOGNITION 12                                                                                                                                                                                                                                                                      |

| CHAPTER TWO – FACE RECOGNITION                                                                                                                                                                                                                                                                         |

|                                                                                                                                                                                                                                                                                                        |

| 2.1 Face Recognition System 12                                                                                                                                                                                                                                                                         |

| 2.1 Face Recognition System                                                                                                                                                                                                                                                                            |

| 2.1 Face Recognition System122.2 Face Recognition Processing132.3 Face Recognition Techniques14                                                                                                                                                                                                        |

| <ul> <li>2.1 Face Recognition System</li></ul>                                                                                                                                                                                                                                                         |

| 2.1 Face Recognition System122.2 Face Recognition Processing132.3 Face Recognition Techniques142.3.1 Principal Component Analysis (PCA)142.3.1.1 Overview of PCA14                                                                                                                                     |

| 2.1 Face Recognition System122.2 Face Recognition Processing132.3 Face Recognition Techniques142.3.1 Principal Component Analysis (PCA)142.3.1.1 Overview of PCA142.3.1.2 Theory of PCA16                                                                                                              |

| 2.1 Face Recognition System122.2 Face Recognition Processing132.3 Face Recognition Techniques142.3.1 Principal Component Analysis (PCA)142.3.1.1 Overview of PCA142.3.1.2 Theory of PCA162.3.1.3 How to use PCA in Face Recognition18                                                                  |

| 2.1 Face Recognition System122.2 Face Recognition Processing132.3 Face Recognition Techniques142.3.1 Principal Component Analysis (PCA)142.3.1.1 Overview of PCA142.3.1.2 Theory of PCA162.3.1.3 How to use PCA in Face Recognition182.3.2 Linear Discriminant Analysis (LDA)19                        |

| 2.1 Face Recognition System122.2 Face Recognition Processing132.3 Face Recognition Techniques142.3.1 Principal Component Analysis (PCA)142.3.1.1 Overview of PCA142.3.1.2 Theory of PCA162.3.1.3 How to use PCA in Face Recognition182.3.2 Linear Discriminant Analysis (LDA)192.3.2.1 Theory of LDA19 |

| 2.3.4.1 Theory of GWT                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

| 2.3.5 Neural Networks                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

|                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| CHAPTER THREE – FINGERPRINT ANALYSIS AND                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| REPRESENTATION                                                                                                                                                                                                                                                                                                                                                                | 28                                                                   |

|                                                                                                                                                                                                                                                                                                                                                                               |                                                                      |

| 3.1 Introduction                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

| 3.2 Fingerprint Image Processing and Feature Extraction                                                                                                                                                                                                                                                                                                                       |                                                                      |

| 3.3 Estimation of Local Ridge Orientation                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| 3.4 Estimation of Local Ridge Frequency                                                                                                                                                                                                                                                                                                                                       |                                                                      |

| 3.5 Singularity and Core Detection                                                                                                                                                                                                                                                                                                                                            |                                                                      |

| 3.5.1 Poincarè Index Method                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

| 3.6 Normalization                                                                                                                                                                                                                                                                                                                                                             |                                                                      |

| 3.7 Minutiae Detection                                                                                                                                                                                                                                                                                                                                                        |                                                                      |

| 3.8 Estimation of Ridge Count                                                                                                                                                                                                                                                                                                                                                 |                                                                      |

| 2.0 Eingernrint Metching                                                                                                                                                                                                                                                                                                                                                      | 38                                                                   |

| 3.9 Fingerprint Matching                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

| 5.9 Fingerprint Matching                                                                                                                                                                                                                                                                                                                                                      |                                                                      |

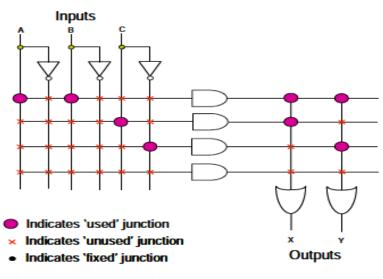

| CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES                                                                                                                                                                                                                                                                                                                                     |                                                                      |

| CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES                                                                                                                                                                                                                                                                                                                                     | 40                                                                   |

| CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES                                                                                                                                                                                                                                                                                                                                     | <b>40</b>                                                            |

| CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES                                                                                                                                                                                                                                                                                                                                     | <b>40</b>                                                            |

| CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES                                                                                                                                                                                                                                                                                                                                     | <b>40</b><br>                                                        |

| CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES<br>4.1 History of Programmable Logic<br>4.2 FPGA Architecture                                                                                                                                                                                                                                                                       | <b>40</b><br>40<br>42<br>42                                          |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES</li> <li>4.1 History of Programmable Logic</li></ul>                                                                                                                                                                                                                                                                       | <b>40</b> 4042424242                                                 |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES</li> <li>4.1 History of Programmable Logic</li></ul>                                                                                                                                                                                                                                                                       | <b>40</b> 40424242424344                                             |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES</li> <li>4.1 History of Programmable Logic</li></ul>                                                                                                                                                                                                                                                                       | 40<br>40<br>42<br>42<br>42<br>43<br>43<br>44                         |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES</li> <li>4.1 History of Programmable Logic</li></ul>                                                                                                                                                                                                                                                                       |                                                                      |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES</li> <li>4.1 History of Programmable Logic</li></ul>                                                                                                                                                                                                                                                                       | 40<br>40<br>42<br>42<br>42<br>43<br>43<br>44<br>45<br>46             |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES.</li> <li>4.1 History of Programmable Logic.</li> <li>4.2 FPGA Architecture.</li> <li>4.2.1 Logic Element (LE)</li> <li>4.2.2 Logic Array Block (LAB)</li> <li>4.3 FPGA Configuration</li> <li>4.3.1 Schematic Design Entry</li> <li>4.3.2 Hardware Description Languages.</li> <li>4.3.3 High-Level Languages.</li> </ul> | 40<br>40<br>42<br>42<br>42<br>43<br>43<br>44<br>44<br>45<br>46<br>47 |

| <ul> <li>CHAPTER FOUR – PROGRAMMABLE LOGIC DEVICES</li> <li>4.1 History of Programmable Logic</li></ul>                                                                                                                                                                                                                                                                       | 40<br>40<br>42<br>42<br>42<br>43<br>43<br>44<br>45<br>46<br>47<br>47 |

| CHAPTER FIVE – FPGA-BASED FACE AND FINGERPRINT                          |        |

|-------------------------------------------------------------------------|--------|

| RECOGNITION SYSTEM DESIGN                                               | 52     |

| 5.1 Face and Fingerprint Recognition System Design on UP3 Development K | Cit 52 |

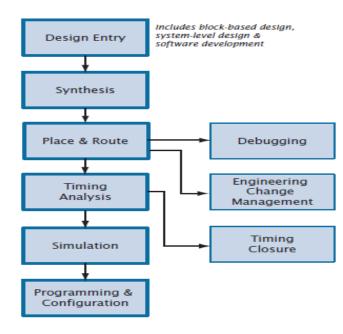

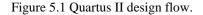

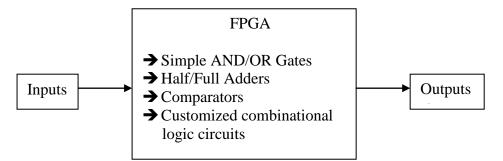

| 5.1.1 Quartus II Software                                               |        |

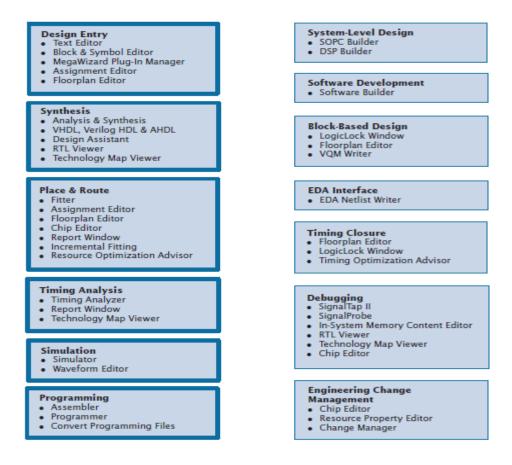

| 5.1.2 Preliminary Study on UP3 Development Kit                          |        |

| 5.1.3 PCA implementation on MATLAB                                      |        |

| 5.1.4 UART                                                              | 62     |

| 5.1.4.1 UART Baud Rate Generator                                        | 63     |

| 5.1.4.2 UART Transmitter                                                | 65     |

| 5.1.4.3 UART Receiver                                                   | 66     |

| 5.1.5 UART Implementation in VHDL                                       | 66     |

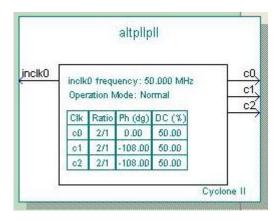

| 5.1.5.1 Baud Generator Design in VHDL                                   | 67     |

| 5.1.5.2 UART Transmitter Design in VHDL                                 | 67     |

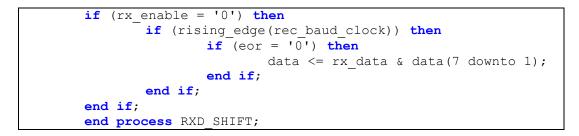

| 5.1.5.3 UART Receiver Design in VHDL                                    | 70     |

| 5.1.6 UART Implementation Results and Findings                          | 72     |

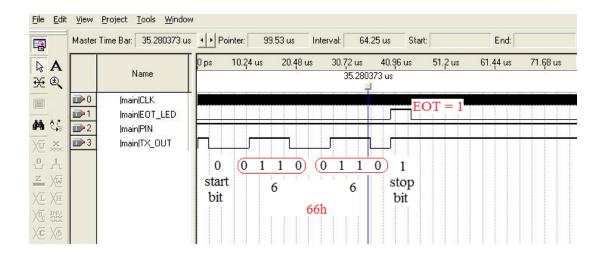

| 5.1.6.1 One Byte Transmitter                                            | 72     |

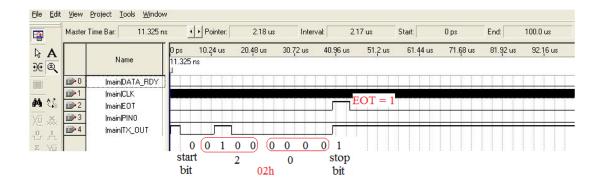

| 5.1.6.2 One Byte Receiver                                               | 73     |

| 5.1.6.3 Array Transmitter                                               | 74     |

| 5.1.6.4 Simulation of Internal Database and Test Comparison             | 75     |

| 5.1.6.5 Comparing Database and Test after Receiving from MATLAB         | 76     |

| 5.1.6.6 Face Recognition System on UP3 Development Kit                  | 77     |

| 5.2 Face and Fingerprint Recognition System Design on DE2-70            | 78     |

| 5.2.1 Hardware Design of Face and Fingerprint Recognition System        | 79     |

| 5.2.2 Implementation of Face Recognition System on DE2-70               | 91     |

| 5.2.2.1 Software Design on DE2-70                                       | 91     |

| 5.2.2.2 Implementation on MATLAB                                        | 95     |

| 5.2.2.3 Preliminary Experiments                                         | 96     |

| 5.2.2.4 Final Implementation                                            | 102    |

| 5.2.2.5 General Performance of the Face Recognition System              | 106    |

| 5.2.3 Implementation of Fingerprint Recognition System on DE2-70        | 108    |

| 5.2.3.1 Fingerprint Scanner                                             | 108    |

| 5.2.3.2 Preliminary Experiments 11                                     | 0  |

|------------------------------------------------------------------------|----|

| 5.2.3.3 Final Implementation 11                                        | 4  |

| 5.2.3.4 General Performance of the Fingerprint Recognition System 11   | 5  |

| CHAPTER SIX – FPGA-BASED MULTIBIOMETRIC RECOGNITION<br>SYSTEM DESIGN11 | 7  |

| 6.1 Implementation of Multibiometric Recognition System on DE2-7011    | 7  |

| 6.2 General Performance of the Multibiometric Recognition System 11    | 9  |

| CHAPTER SEVEN – CONCLUSIONS120                                         | 0  |

| 7.1 Summary of the Project                                             | .0 |

| 7.2 Advantages - Disadvantages                                         | 1  |

| 7.3 Troubleshooting 12                                                 | 2  |

| 7.4 Cost Analysis 12                                                   | 3  |

| 7.5 Future Work                                                        | 3  |

| REFERENCES                                                             | 4  |

| APPENDIX                                                               | 8  |

### CHAPTER ONE INTRODUCTION

#### **1.1 Biometric Systems**

Biometric recognition term refers to the use of distinctive physiological and behavioral characteristics that are called biometric identifiers for automatically recognizing individuals (Maltoni, Maio, Jain, & Prabhakar, 2003). A number of biometric technologies have been developed and several of them are being used in a variety of applications in differet areas. Among these, face, iris, fingerprints, speech and hand geometry are the ones that most commonly used in biometric systems. Each biometric has its strengths and weakness, so choice of a particular biometric typically depends on the requirements of an application.

A biometric system is a pattern recognition system that responsible for recognizing a person by determining the authenticity of a specific physiological and/or behavioral characteristic possessed by that person. The most important issue in designing a practical biometric system is to determine how this biometric individual is recognized. Depending on the application, a biometric system may be called a verification system or an identification system:

• a verification system authenticates a person's identity by comparing the captured individual characteristic with his/her own biometric template(s) that is stored in the system. One-to-one comparison is done to determine whether the identity claimed by the individual is true. A verification system either rejects or accepts the user,

• an identification system recognizes an individual characteristic by searching the entire template database. One-to-many comparisons is done to establish the identity of the individual. The identification system establishes a subject's identity without the subject having to claim an identity.

### **1.2 Multibiometric Systems**

Most of the biometric systems deployed in real world are unimodal and they are relied on the evidence of a single source of information. Unimodal biometric systems have to contend with a variety of problems such as noisy data, intra-class variations, spoof attacks and unacceptable error rates (Ross, & Jain, 2004). Multimodal or multibiometric systems, which include multiple sources of information, are offered to overcome these limitations in unimodal biometric systems.

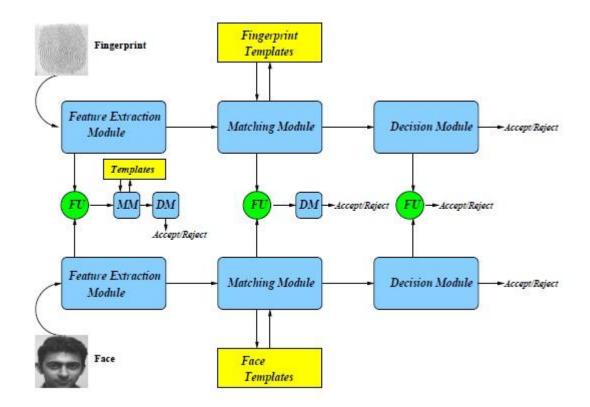

Multibiometric systems represent the fusion of two or more unimodal biometric systems. The fusion can occur at the data or feature level, match score level and decision level. Figure 1.1 shows the levels of fusion in a biomodal biometric system (Ross, & Jain, 2004). Note that; FU, MM and DM stand for fusion, matching and decision module respectively in Figure 1.1.

Figure 1.1 Levels of a fusion in a biomdoal biometric system (Ross, & Jain, 2004).

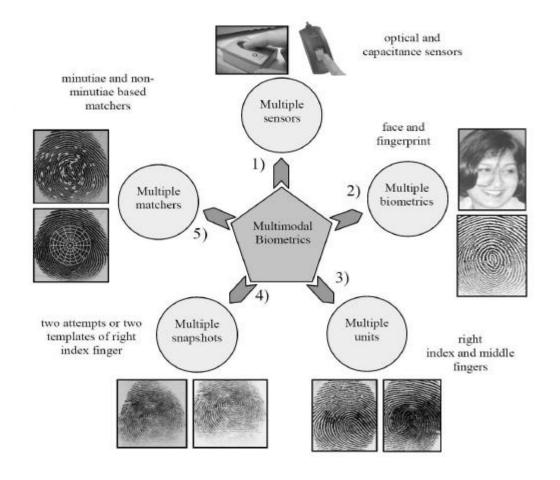

Depending on the number of traits, sensors, and feature sets used, a variety of scenarios are possible in a multimodal biometric system (Ross, & Jain, 2004). Figure 1.2 shows that these various scenarios (Prabhakar, & Jain, 2002);

- multiple sensors for tracking the same biometric behavior such as using optical and capacitive sensors together;

- 2) multiple biometrics for the same person such as using face and fingerprint;

- 3) multiple units such as right index and middle fingers of a person;

- multiple snapshots of the same biometric such as taking for two templates of the right finger of a person

- 5) multiple matchers such as using minutiae and non-minutiae based matchers are the examples of the applications of multibiometric systems.

Figure 1.2 Scenarios in a multimodal biometric system (Prabhakar, & Jain, 2002).

Several factors should be considered when designing a multibiometric system. Some of these factors are;

- the choice and the number of biometric behaviors,

- the level in biometric system at which information provided by multiple types should be integrated,

- the methodology adopted to integrate the information,

- the cost versus matching performance trade-off,

- system is user friendly or not (Anwar, Rahman, & Azad, 2009).

By combining multiple sources of information, these systems improve matching performance, increase population coverage, deter spoofing, and facilitate indexing (Ross, & Jain, 2004). So, multibiometric systems are expected to be more reliable due to presence of multiple independent pieces of evidence.

#### **1.3 History of Face Recognition Systems**

The first way to do face recognition is to look at the major features of the face and compare these features with the same features on the other faces. During 1964 and 1965, Bledsoe, along with Helen Chan and Charles Bisson, worked on using the computer to recognize human faces (Bledsoe 1966a, & 1966b; Bledsoe, & Chan 1965). By using a semi-automated machine, later called man-machine, marks were made on photographs. These marks are used to locate major features of the faces such as mouths, noses, eyes and ears. The distances and ratios were computed by using these marks, then these are compared to reference enrollment data.

In the early 1970's Goldstein, Harmon and Lesk used 21 subjective markers such as hair color and lip thickness to create a face recognition system. (Goldstein, Harmon, & Lesk, 1971). Because of difficulties in order to automate due to subjective nature, many of the measurements were still made by hand. A more automated approach to recognition began with Fisher and Elschlagerb just a few years after the Goldstein paper. This approach measured the features above using templates of features of different pieces of the face and them mapped them all onto a global template. After continued research it was found that these features do not contain enough unique data to represent an adult face. Another approach is the Connectionist approach, which seeks to classify the human face using a com-bination of both range of gestures and a set of identifying markers. This is usually implemented using 2-dimensional pattern recognition and neural net principles. Most of the time this approach requires a huge number of training faces to achieve decent accuracy; for that reason it has yet to be implemented on a large scale (Escarra, Robinson, Krueger, & Kochelek, 2004).

The major problem of the early face recognition solutions is the most of feature measurements and face locations were computed manually. In 1980's, the first fully auotomated face recognition method is created depending on statistical approach. In 1988, Kirby and Sirovich applied principle component analysis at Brown University. This was considered a milestone in face recognition, because their approach is showed that less than one hundred values were required to accurately code a suitably aligned and normalized face image (Sirovich, & Kirby, 1987).

In 1991, Turk and Pentland discovered that the residual error coud be used to detect face in images while using the eigenfaces technique (Turk, & Pentland, 1991). This discovery was enabled to develop reliable real-time automated face recognition systems and increase significant interest on face recognition automation field. Since then, many different approaches have been published for face recognition over the years such as Neural Network, Fisher Linear Discriminant Model (FLD), Dynamic Link Architectures (DLA), Hidden Markov Models, Gabor Wavelet Transform, Elastic Bunch Graph. Some of these techniques were covered on Section 2.3.

The face recognition technology first captured the public's attention from the media reaction to a trial implementation at the January 2001 Super Bowl, which captured surveillance images and compared them to a database of digital mugshots.

This demonstration initiated much-needed analysison how to use the technology to support national needs while being considerate of public's social and privacy concerns. Today, face recognition technolgy is being used to combat passport fraud, support law enforcement, identify missing children, and minimize benefit/identify fraud (Smith, Ross, & Colbry, 2006).

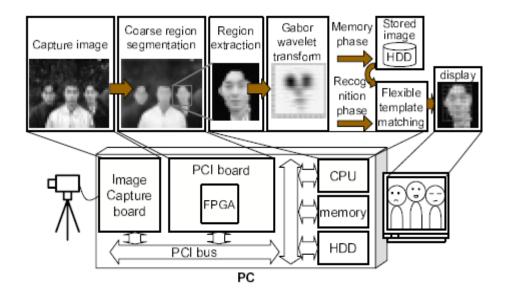

Increase in the automation of face recognition provides hardware solutions such as application specific integrated circuit (ASIC) designs and field programmable gate arrays (FPGA). Using FPGA has many benefits over ASICs, because of low cost rapid prototyping and flexibility. One of the first publications implementing FPGA as a hardware is released by T. Nakano, T.Morie and A.Iwata in 2003. The face/object recognition system using coarse region segmentation and flexible template matching was presented and the resistive-fuse network circuit was implemented in an FPGA by a pixel serial approach, and coarse region segmentation of real images with  $64 \times 64$  pixels at the video rate was achieved. The flexible template matching using dynamic-link architecture was performed in the PC system. Figure 1.3 shows this implementation (Nakano, Morie, & Iwata, 2003).

Figure 1.3 The face/object recognition system (Nakano, Morie, & Iwata, 2003).

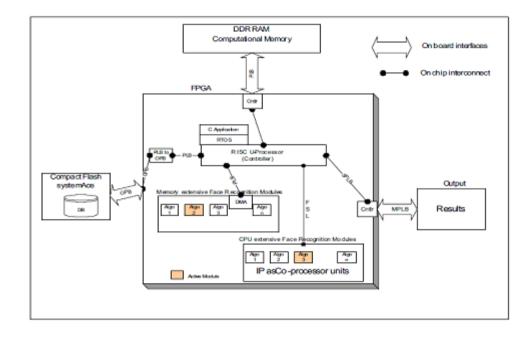

One of the latest research by I. Sajid, M. M. Ahmed, I. Taj, M. Humayun, & F. Hameed in 2008, presents a fixed point tecnique with software hardware co-design (SHcoD) due to the floatingpoint operations based on eigenvalue algorithms are complex in terms of hardware.

Figure 1.4 Fpga-based system architecture (Sajid, Ahmed, Taj, Humayun, & Hameed, 2008).

They have also stated that fixed point implementation of householder (HH) algorithm saves thousands of machine cycles in the cost of losing 0.008 percent weight in highest three Eigen value. The system architecture can be seen in Figure 1.4 (Sajid, Ahmed, Taj, Humayun, & Hameed, 2008).

### **1.4 History of Fingerprinting**

Human fingerprints have been discovered on a large number of archaeological and historical items. These findings provide evidence to show that ancient people were aware of the individuality of fingerprints, such awareness does not appear to have any scientific basis (Lee, & Gaensslen, 2001). The modern scientific fingerprint technique was first initiated in the start of sixteenth century. In 1684, Nehemiah

8

Grew, published the first scientific paper reporting his systematic study on the ridge, furrow, and pore structure in fingerprints (Lee, & Gaensslen, 2001).

Since then, a large number of researchers interested in fingerprint studies. In 1788, a detailed description of the anatomical formations of fingerprints was made by Mayer (Moenssens, 1971). Thomas Bewick began to use his fingerprint as his trademark in 1809. This is believed to be one of the most important milestones in the scientific study of fingerprint recognition (Moenssens, 1971). In 1823, Purkinje proposed the first fingerprint classification scheme, that classified fingerprints into nine categories according to the ridge structures (Moenssens, 1971). In 1880, Henry Fauld, first scientifically suggested the individuality of fingerprints based on an empirical observation and Herschel asserted that he had practiced fingerprint recognition for about 20 years (Lee, & Gaensslen, 2001 and Moenssens, 1971). In the late nineteenth century, Sir Francis Galton conducted an extensive study on fingerprint matching. Important advance in fingerprint recognition was made in 1899 by Edward Henry. Henry established the well-known "Henry system" of fingerprint classification (Lee, & Gaensslen, 2001).

In the early twentieth century, fingerprint recognition was formally accepted as a valid personal identification method and became a standard routine in forensics (Lee, & Gaensslen, 2001). Fingerprint identification agencies were set up worldwide and criminal fingerprint databases were established (Lee, & Gaensslen, 2001). Various fingerprint recognition techniques such as fingerprint acquisition, fingerprint classification, and fingerprint matching were developed. For example, the FBI fingerprint identification division was set up in 1924 with a database of 810,000 fingerprints (Federal Bureau of Investigation, 1984).

Starting in the early 1960s, the FBI, Home Office in the UK, and Paris Police Department began to invest a large amount of effort in developing automatic fingerprint identification systems (Lee, & Gaensslen, 2001). Based on the observations of how human fingerprint experts perform fingerprint recognition, three

major problems in designing automatic fingerprint identification systems (AFISs) were identified and investigated: digital fingerprint acquisition, local ridge characteristic extraction, and ridge characteristic pattern matching and their efforts were so successful that today almost every law enforcement agency worldwide uses an AFIS (Maltoni, Maio, Jain, & Prabhakar, 2003).

Automatic fingerprint recognition technology has now rapidly grown in civilian applications and fingerprint-based biometric systems are so popular for their recognition rate.

### 1.5 Aim of Thesis

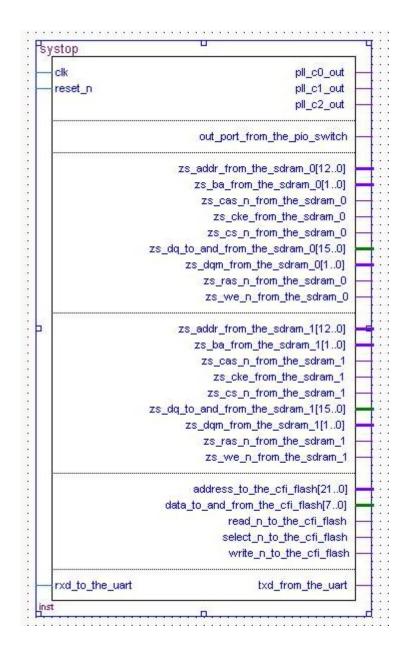

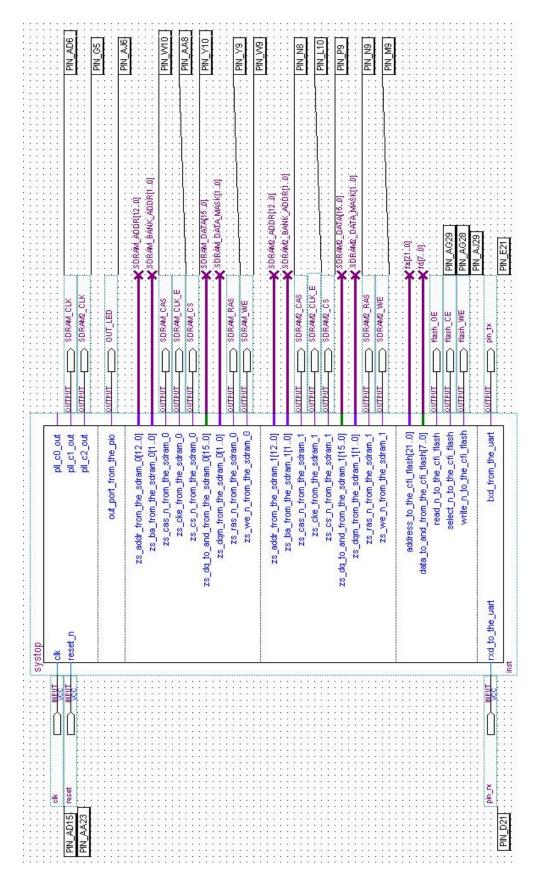

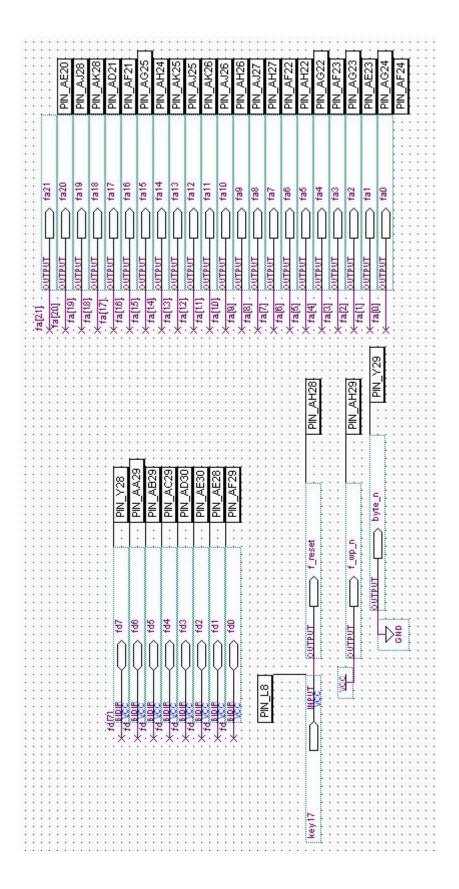

The aim of the thesis is to create a fingerprint and face recognition system which is established on a Field Programmable Gate Array (FPGA). Principle Component Analyis (PCA), is used for extracting features. The fingerprint and face images are transformed into PCA basis subspace that is composed from eigenvalues and eigenvectors. System development in FPGA includes embedded microprocessor design, SDRAM implementation for memory needs, CFI Flash implementation for storing PCA results and communication interface for host computer. These parts of the design are discussed to develop usability and compability of the system. Comparision methods are used to identify the user in the most accurate way.

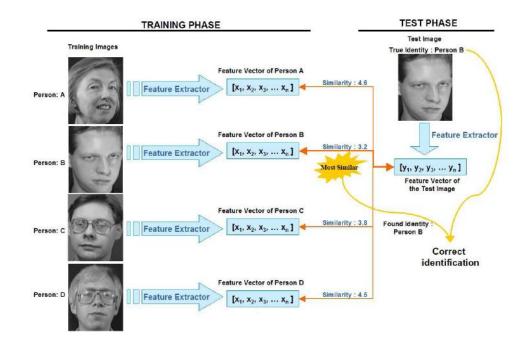

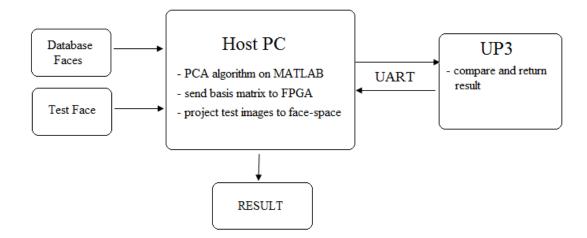

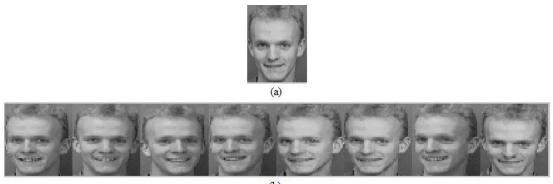

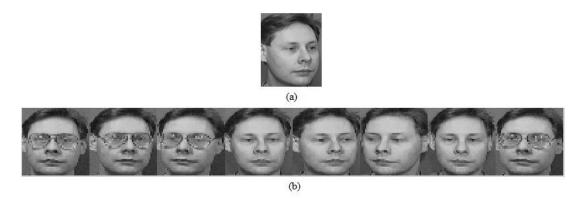

This thesis proposes a system to acquire a face or a fingerprint image of any user and process it to understand if he/she is one of people in the training database. This project are combined with two main parts. First and second part can be called as offline-training and online-test respectively. Figure 1.5 shows these two parts briefly for face recognition.

In the offline-training part for face recognition, face photos are taken from people and stored in the host computer. Then, images are resized to increase calculation speed and combined in one database matrix in MATLAB. This database matrix are sent to FPGA via serial port using RS-232 protocol. At the end of this transmission, PCA feature extraction methods are started in FPGA to create PCA basis and project database images to face subspace. At the end of offline-training part, PCA basis matrix and projected training matrix of database images are stored in CFI Flash memory. The offline-training part for fingerprint recognition is too similar to the face recognition and the only difference is the device that used for acquiring images. Face images are taken from web-camera and fingerprints are taken via fingerprint reader.

Figure 1.5 Offline-training and online test parts for face recognition.

Online-test part starts to procedure by taking a photo or a fingerprint of tester. This image is read, resized and sent to FPGA by MATLAB like in the offline-training method. After FPGA gets the test image, FPGA restores PCA basis matrix and projected training matrix of database images from CFI Flash. After projecting test image to face or fingerprint subspace by multiplying PCA basis matrix, it is compared with projected training matrix and returns result to the host computer via serial port.

After the implementation of the face and fingerprint recognition systems separately, a multibiometric recognition system, which offers more reliable recognition, is implemented by combining these two systems.

### **1.6 Outline of Thesis**

This thesis composed of six chapters including the Introduction. Chapter 2 reviews face recognition processes and Chapter 3 summarizes fingerprint analysis and representation techniques. In Chapter 4, programmable logic devices are introduced with the devices that are used throughout project. Chapter 5 summarizes the system and explains the operation. The preliminary experiments and final results are also presented in this chapter. After completing the design of face and fingerprint recognition systems separately, they are combined together to construct a multibiometric recognition system. Chapter 6 describes this implementation. The last chapter of the thesis, Chapter 7, includes conclusions, advantages and disadvantages of the system, future works. The algorithm of whole system is in the Appendix part of the thesis.

### CHAPTER TWO FACE RECOGNITION

#### 2.1 Face Recognition System

Face recognition systems automatically identify faces from images and videos. Two operation modes are defined for these systems: face verification and face identification, which are described briefly as follows:

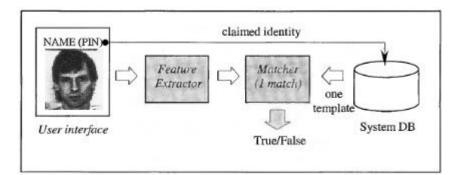

### a) Face Verification:

The verification task is responsible for verifying faces at the point of access. The operation of verification system is shown in Figure 2.1. The user enters his/her name or PIN (Personal Identification Number) through a keyboard or a keypad and the biometric reader the characteristic of the face to be recognized and converts it to a digital format. The digital formatted face data is processed by the feature extractor to produce a compact digital representation. The resulting representation is fed to the feature matcher to compare it against the template of a single user which is retrieved from the system database based on the user's PIN.

Figure 2.1 Face verification system.

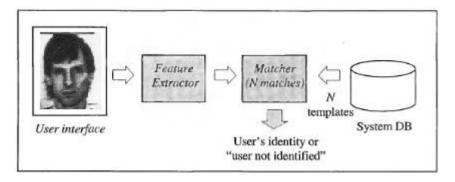

### **b)** Face Identification:

PIN isn't provided by the user in the face identification. This task is to compare the representation of the input faces against the templates of all the users in the system database. This system identifies of an enrolled user or producing an alert message such as "user not identified".

Figure 2.2 Face identification system.

### 2.2 Face Recognition Processing

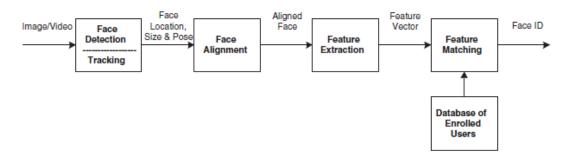

Face recognition is a visual pattern recognition problem. A face is identified from two-dimensional images which are extracted from three-dimensional images. Since these real face images vary with pose, expression, illumination and so on, the problem is a challenging one. A face recognition process consists of four processes and these are shown in Figure 2.3.

Figure 2.3 Face recognition processing flow scheme (Li, & Jain, 2004).

Face detection segments the face areas from the background. In the case of video, the detected faces may need to be tracked using a face tracking component. Face alignment is aimed at achieving more accurate localization and at normalizing faces thereby whereas face detection provides coarse estimates of the location and scale of each detected face. Facial components, such as eyes, nose, and mouth and facial outline, are located; based on the location points, the input face image is normalized with respect to geometrical properties, such as size and pose, using geometrical transforms or morphing. The face is usually further normalized with respect to photometrical properties such illumination and gray scale. After a face is normalized geometrically and photometrically, feature extraction is performed to provide effective information that is useful for distinguishing between faces of different persons and stable with respect to the geometrical and photometrical variations. For face matching, the extracted feature vector of the input face is matched against those of enrolled faces in the database; it outputs the identity of the face when a match is found with sufficient confidence or indicates an unknown face otherwise (Li, & Jain, 2004).

### 2.3 Face Recognition Techniques

This section try to describe the basic feature extraction and face recognition techniques such as principal component analysis (PCA), independent component analysis (ICA), linear discriminant analysis (LDA), Elastic Bunch Graph Matching (EBGM) and neural networks with mathematical theories.

### 2.3.1 Principal Component Analysis (PCA)

PCA algorithm is common feature extraction technique which is used for face recognition. PCA is also used in this thesis, thus this technique is described in detail. First section is an overview of PCA, second section shows the mathematical background and the last section describes the usage of PCA in face recognition field.

### 2.3.1.1 Overview of PCA

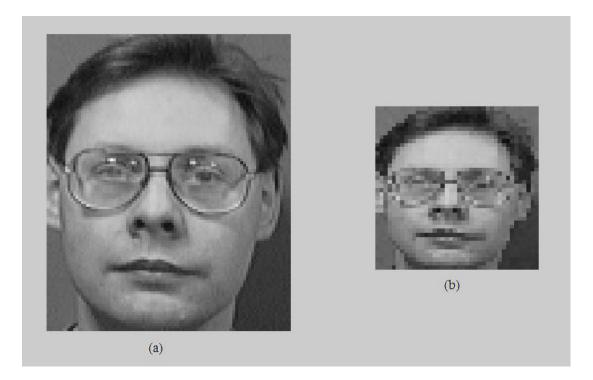

PCA is a standard linear algebra technique and pioneered by Kirby and Sirovich in 1988. This technique is commonly referred to as the use of eigenfaces in face recognition. To use this technique, database and test images must be at the same size and must first be normalized to line up the eyes and mouth of the subjects within the images. After normalization, PCA is used to reduce the dimension of the data by means of data compression basics. This operation reveals the most effective low dimensional structure of the facial patterns. The reduction in dimensions removes the unuseful information and decomposes the face into orthogonal (or uncorrelated) components, which are also known as eigenfaces.

Each face image may be represented as a weighted sum of the eigenfaces and these eigenfaces are stored in a 1D array. This 1D array also known as a feature vector in PCA literature. When test image is compared to database image, this feature vector is used to measure the distance. The PCA approach typically requires the full frontal face to be presented each time; otherwise the image results in poor performance (Bolme, Beveridge, Teixeira, & Draper, 2003). PCA technique can reduce the data needed to identify the individual to 1/1000<sup>th</sup> of the data presented.

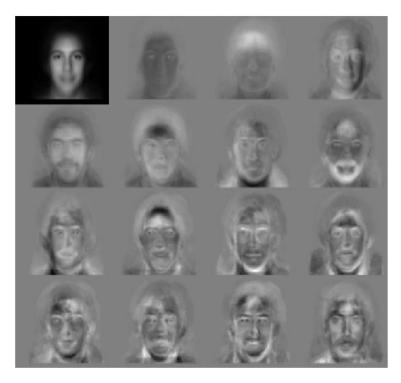

Figure 2.4 shows an example of eigenfaces (MIT Media Laboratory, 2002). Feature vectors are derived using eigenfaces.

Figure 2.4 An example of eigenfaces.

### 2.3.1.2 Theory of PCA

Let the training set of *M* face images be  $I_1$ ,  $I_2$ ,  $I_3$ , ...,  $I_M$ . The average of the training set is,  $\mu$ ,

$$\mu = \frac{1}{M} \sum_{n=1}^{M} I_n \tag{2-1}$$

The difference of each image from the average is defined as;

$$\theta_i = I_i - \mu \tag{2-2}$$

This set of very large vectors is then subject to PCA, which seeks a set of M orthonormal vectors,  $u_n$ , which are describing the distribution of whole data. The *k*th vector of this vector,

$$\lambda_k = \frac{1}{M} \sum_{n=1}^M (u_k^T \theta_n)^2$$

(2-3)

is a maximum subject to

$$u_l^T u_k = \zeta_{lk} = \begin{cases} 1, & \text{if } l = k \\ 0, & \text{otherwise} \end{cases}$$

(2-4)

The vectors  $u_k$  are eigenvectors and the scalars  $\lambda_k$  are eigenvalues of the covariance matrix which is shown in the following,

$$C = \frac{1}{M} \sum_{n=1}^{M} \theta_n \theta_n^T$$

$$= A A^T$$

(2-5)

where *C* is the covariance matrix and  $A = [\theta_1, \theta_2, ..., \theta_M]$ .

The matrix *C*, is  $N^2$  by  $N^2$ , and determining the  $N^2$  eigenvectors and eigenvalues is an intractable task for typical image sizes, so a computationally feasible method to find these eigenvectors must be implemented. If the number of data points in the image space is less than the dimension of the space ( $M < N^2$ ), there is only M - 1, rather than  $N^2$  meaningful eigenvectors (Turk and Pentland, 1991). By using this approach the eigenvectors  $v_i$  of  $A^T A$  is,

$$A^T A v_i = \beta_i v_i \tag{2-6}$$

multipliying both sides by A,

$$AA^{T}Av_{i} = \beta_{i}Av_{i}$$

(2-7)

Eq. (2-7) shows that  $Av_i$  are the eigenvectors of  $C = AA^T$ . By using this analysis, Mx M matrix,  $L = A^T A$  is constructed. The L is,

$$L_{mn} = \theta_m^T \theta_n \tag{2-8}$$

and shows the *M* eigenvectors,  $v_l$ , of *L*. These vectors are used to determine the linear combinations of the *M* training set face images to form the eigenfaces  $u_l$ .

$$u_l = \sum_{k=1}^{M} v_{lk} \theta_k, \qquad l = 1, 2, ..., M$$

(2-9)

With this analysis the calculations are greatly reduced, from the order of the number of pixels in the images  $(N^2)$  to order of the number of images in the training set (M) and in practice, the training set of face images will be relatively small and the calculations become quite managable (Turk and Pentland, 1991).

To create a face space from M number of the face images, first L matrix  $(M \times M)$  must be calculated. This L matrix has M eigenvectors.  $M_1$  significant eigenvectors are chosen from this L matrix which are containing the highest associated eigenvalues. Then, by combining the normalized training images according to Eq. (2-9) to produce the eigenfaces  $u_k$ .

For the test step, first the new face image  $(I_T)$  is projected into facespace by a simple operation,

$$\omega_k = u_k (I_T - \mu)$$

for  $k = 1, 2, ..., M_1$  (2-10)

and  $\omega$  is the weights and these weights form the pattern vector,  $\varphi^{T}$ ,

$$\varphi^{T} = [\omega_{1}, \omega_{2}, ..., \omega_{M_{1}}]$$

(2-11)

The pattern vector describes the contribution of each eigenface in representing the input face image. After generating pattern vector, the simplest method for determining which face class provides the best description of an input face image is to find the face class k which minimizes the Euclidean distance,  $\varepsilon$ ,

$$\mathcal{E}_{k} = \left\| \left( \varphi - \varphi_{k} \right) \right\|^{2} \tag{2-12}$$

where  $\varphi_k$  is a vector describing the *k*th face class and the face classes  $\varphi_i$  are calculated by averaging the results of the eigenfaces over a small number of face images of each individual. The minimum  $\varepsilon_k$ , if provides the recognition condition under a pre-determined threshold value, *k*th person is determined the output of recognition system.

### 2.3.2 Linear Discriminant Analysis (LDA)

LDA is a statistical approach for classifying samples of unknown classes based on the training samples with known classes (Bolme, Beveridge, Teixeira, & Draper, 2003). LDA is the technique which aims to maximize variance across the users or formerly named between-classes, and minimize variance within the users which is also expressed within-class formerly.

In the Figure 2.5, an example of six classes using LDA is shown (Lu, Plataniotis, & Venetsanopoulos, 2003). In this figure, each block represents a class. There are large variances between-classes, but the variance within-classes is very little. When dealing with high dimensinal face data, this technique faces the sample size problem that arises where there are a small number of available training samples compared to the dimensionality of the sample space (Lu, Plataniotis, & Venetsanopoulos, 2003).

Figure 2.5 An example of six classes using LDA.

### 2.3.2.1 Theory of LDA

As mentioned above, all instances of the same person's face as being in one class and the faces of different subjects as being in different class for all subjects in the training must be defined before computing LDA. LDA is a class specific method that represents data set make it useful for classification. Given a set of N imgaes  $\{x_1, x_2, ..., x_n\}$  where each image belongs to one of c classses  $\{X_1, X_2, ..., X_c\}$ . LDA selects a linear tranformation matrix W that is the ratio of the between-class scatter and the with-in class scatter is maximized.  $S_B$  is the between-class scatter matrix which represents the scatter of the conditional mean vectors,  $\mu_i$ 's; around the overall mean vector,  $\mu$ .  $S_B$  can be expressed by the following formula;

$$S_{B} = \sum_{i=1}^{c} N_{i} (\mu_{i} - \mu) (\mu_{i} - \mu)^{T}$$

(2-13)

where  $\mu_i$  denotes the mean of image class  $X_i$ ,  $\mu$  denotes the mean of entire data set,  $N_i$  denotes the number of images in class  $X_i$ .

$S_W$  is the within-class scatter matrix which represents the average scatter of the sample vectors x of different class  $C_i$  around their respective mean  $\mu_{i;}$

$$S_{W} = \sum_{i=1}^{c} \sum_{x_{k} \in X_{i}} (x_{k} - \mu_{i}) (x_{k} - \mu_{i})^{T}$$

(2-14)

If the within-class scatter matrix  $S_W$  is not singular, LDA finds an orthonormal matrix  $W_{opt}$  which maximizes the ratio of the determinant of the between-class scatter matrix to the determinant of the within-class scatter matrix. This matrix can be expressed by the following formula;

$$W_{opt} = \arg \max \frac{|W^T S_B W|}{|W^T S_W W|} = [w_1 \ w_2 \ \dots \ w_m]$$

(2-15)

The set of solution  $\{w_i \mid i = 1, 2, ..., m\}$  is that of generalized eigenvectors of  $S_B$  and  $S_W$  corresponding to the *m* largest eigenvalues  $\{\lambda_i \mid i = 1, 2, ..., m\}$ , which can be shown that as in following;

$$S_B w_i = \lambda_i S_W w_i$$

where  $i = 1, 2, ..., m$  (2-16)

In face recognition applications, generally  $S_W$  is singular, so to overcome this singularity, PCA algorithm is first used to reduce the vector dimensions. Combining PCA and LDA, first input image *x* projected into face space *y*, then projected into classification space *z*;

$$y = \theta^{T} x \quad \text{(only PCA)}$$

$$z = W_{x}^{T} x \quad \text{(only LDA)}$$

$$z = W_{y}^{T} y \quad \text{(PCA + LDA)}$$

(2-17)

### 2.3.3 Independent Component Analysis (ICA)

ICA is another algorithm for face recognition. To better understand the concept, it is useful to compare ICA with PCA. PCA depends on the pairwise relationships between pixels, but ICA depends on the higher order relationships among pixels in the image database. So that, PCA can only represent second order interpixel relationships, or relationships that capture the amplitude spectrum of an imgage but not its phase spectrum. On the other hand, ICA use high order relationships between the pixels and ICA algorithms are capable of capturing the phase spectrum (Bartlett, Movellan, & Sejnowski, 2002).

In the ICA implementation of face recognition, input face image represented as an n-dimensional random vector. Then, PCA is used to reduce this random vector, without losing the higher order statistical components. After that, covariance matrix of the result is calculated and factorized form of covariance matrix is obtained. Whitening, rotation and normalization are performed respectively to obtain the face space of the individuals. Because of using high order relationships between pixels, ICA is robust in the presence of noise.

ICA of a random vector searches for a linear transformation which minimizes the statistical dependence between its components (Comon, 1994). Let, the image is represented by a random vector,  $X \in \mathbb{R}^N$ , where *N* is the dimensionality of the image space. The vector is formed by concatenating the rows or the coloumns of the image which may be normalized to have a unit norm and/or an equalized histogram (Liu, & Wechsler, 1999). The covariance matrix of *X* can be expressed by using expectation operator, *E*(.), as in the following;

$$C_X = E\{[X - E(X)][X - E(X)]^T\}$$

(2-18)

where  $C_X \in \mathbb{R}^{N \times N}$ . The ICA of *X* factorizes the covariance matrix into the following expression;

$$C_{X} = F\Delta F^{T}$$

(2-19)

where  $\Delta$  is diagonal real positive and *F* transforms the original data set *X* to new data set *Z* which are independent or the most independent possible data set. *Z* can be expressed as;

$$X = FZ \tag{2-20}$$

To find the transformation F, Comon developed an algorithm that consists of three operations: whitening, rotation and normalization (Comon, 1994). The whitening operation transforms a random vector X to U which has a unit covariance matrix and U can be expressed by the following formula;

$$X = \varphi A^{1/2} U \tag{2-21}$$

where  $\varphi$  and A are derived by solving the following eigenvalue operation;

$$C_X = \varphi A \varphi^T \tag{2-22}$$

where  $\varphi = [\varphi_1, \varphi_2, ..., \varphi_N]$  is an orthonormal eigenvector matix and  $A = diag \{\lambda_1, \lambda_2, ..., \lambda_N\}$  is a diagonal eigenvalue matrix of  $C_X$ . After whitening operation, rotation operations performs source separation by minimizing the mutual information approximated using high order cumulants to derive independent components. Finally, the normalization operation derives unique independent components in terms of orientation, unit norm, and order of projections (Comon, 1994).

### 2.3.4 Elastic Bunch Graph Matching (EBGM)

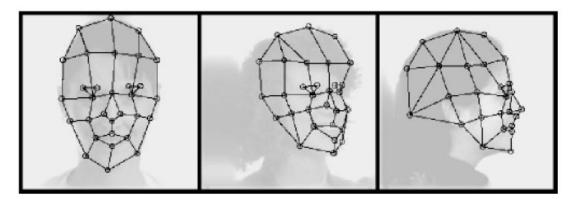

This algorithm relies on the concept of the non-linear characteristics of the real face images, such as pose, expression and variations in illumination. Because, these non-linear characteristics are not addressed by the linear analysis methods, such as PCA and LDA. An example of elastic bunch graph matching is shown in Figure 2.6 (Wiskott, 1996).

Figure 2.6 Elastic bunch graph matching (EBGM).

Gabor Wavelet Transform is used to create a dynamic link architecture that projects the face image onto an elastic grid. The nodes on the elastic grid that are notated by the circles in the previous figure, are formerly called as gabor jets. Gabor jets describe the image behaviour around a given pixel. This is the result of a convolution of the image with Gabor filter. Gabor filter is used to extract features and detect shapes. Recognition is based on comparing Gabor filter response on each Gabor node.

The difficulty with his method is the requirement of accurate landmark localization, which can sometimes be achieved by combining PCA and LDA methods (Bolme, Beveridge, Teixeira, & Draper, 2003). As mentioned above, EBGM based on Gabor Wavelet Transform (GWT), so in the next section the thery of GWT is described.

### 2.3.4.1 Theory of GWT

Dennis Gabor proposed Gabor functions as a tools for signal detection under noise effect. Gabor showed that the conjonit time-frequency domain for 1D signals must be quantized so that no signal or filter can occupy less than certain minimal area in it (D. Gabor, 1946). Gabor also discovered that Gaussian modulated complex exponentials provide the best trade off between frequency and time resolution. Gabor functions are generalized and reorganized to 2D by Daugman, to use in computer vision applications which is expressed below (Daugman, 1980);

$$G_{i}(\vec{x}) = \frac{\left\|\vec{k}_{i}\right\|^{2}}{\sigma^{2}} e^{-\frac{\left\|\vec{k}_{i}\right\|^{2} \left\|\vec{x}\right\|^{2}}{2\sigma^{2}}} \left[e^{j\vec{k}_{i}\vec{x}} - e^{\frac{\sigma^{2}}{2}}\right]$$

(2-23)

where *Gi* is a plane wave characterized by the vector *ki* enveloped by a Gaussian function and  $\sigma$  is the standard deviation of this Gaussian envelope. The center frequency of the *i*th filter is given by the characteristic wave vector which have a scale  $k_{\nu}$  and orientation  $\theta_{\mu}$ ,

$$k_{i} = \begin{pmatrix} k_{ix} \\ k_{iy} \end{pmatrix} = \begin{pmatrix} k_{v} \cos \theta_{\mu} \\ k_{v} \sin \theta_{\mu} \end{pmatrix}$$

(2-24)

Daugman proposed that an ensemble of simple cells is best modeled as a family of 2D Gabor wavelets sampling the frequency domain in a log-polar manner (Daugman, 1980). This is equivalent to coherent states generated by rotation and dilation. The decomposition of an input image *I* into these states is called the wavelet transform and expressed as;

$$R_{i}(\vec{x}) = \int I(\vec{x}) G_{i}(\vec{x} - \vec{x}) d\vec{x}$$

(2-25)

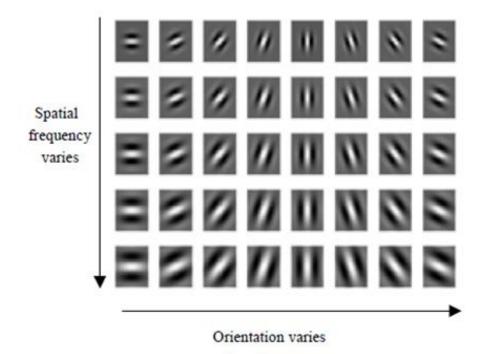

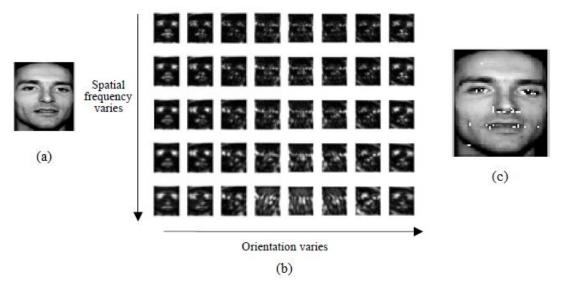

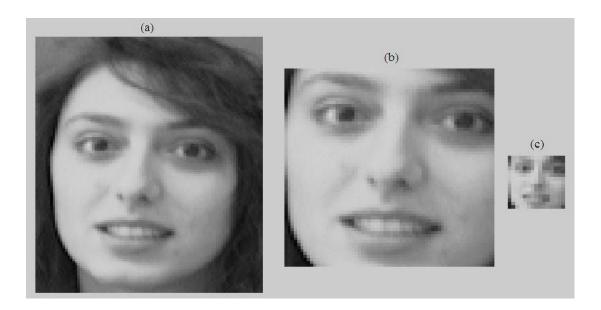

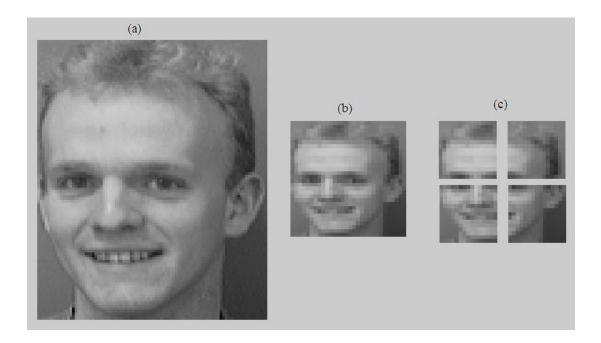

Combining Eq. (2-24) and Eq. (2-25), Gabor wavelets are used first by determining wave vector scale  $k_v$  and orientation  $\theta_{\mu}$ . Kepenekci show that Gabor filters with spatial frequency (v = 0, ..., 4) and 8 orientation ( $\mu = 0, ..., 8$ ) in Figure 2.7 and convolving the input image (Figure 2.8a) with Gabor filters (Figure 2.8b) captures the whole frequency spectrum (Kepenekci, 2001).

Figure 2.7 Gabor filters correspond to 5 spatial frequency and 8 orientation.

From the responses of the face image to Gabor filters, peaks are found by searching the locations (Figure 2.8c) by using windowing methods to find eyes, nose and mouth in the face (Kepenekci, 2001).

Figure 2. 8 (a) An example face image from Stirling database (b) Filter responses (c) High energized points of Gabor wavelet responses

### 2.3.5 Neural Networks

Most of the face recognition systems use smart algorithms to recognize the faces from the extracted features such as eigenfaces. One of the common technique is the artificial neural networks. This algorithm is biogogically inspired and based on the functionality of neurons. The equivalent of neurons in neural network are perceptrons. Neurons sum the strengths of all electric inputs. Similarly, perceptrons generates a weighted sum on their numerical inputs. A neural network is formed for each person in the face database by using these perceptrons.

The neural networks usually consist of three or more layers (Li, & Areibi, 2004). First, database images are dimensionally reduced by using PCA. The input layer of neural network takes these reduced images. The output layer of a neural network produces a numerical value between -1 and 1. In between of these two layers, there exist one or more hidden layers which are depend on the application. When using neural network for face recognition, using one hidden layer provides a good balance between accuracy and complexitiy. Increasing the number of hidden layer, training time of the system exponentially increases. When the neural network is formed for each person, first it must be trained to recognize that person. The most common training method is the back propagation algorithm (Li, & Areibi, 2004). By using this algorithm, the weights of the connections between neurons are set. The result of these connections are high output value (near to 1) belong to the person it represents and low output value (near to -1) for other people. In the recognition face, neural network system returns the highest numerical output for this person.

The biggest problem of neural networks is that, there is no clear method to find the initial network topologies. Since training takes a long time, experimenting with such topologies becomes a difficult task (Li, & Areibi, 2004). Another main issue occurs when neural networks are tried to use online training, time consuming task and the difficulty of adding a new person to database is not well suited for real-time applications.

# CHAPTER THREE FINGERPRINT ANALYSIS AND REPRESENTATION

#### **3.1 Introduction**

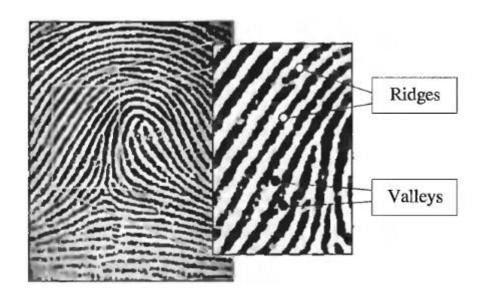

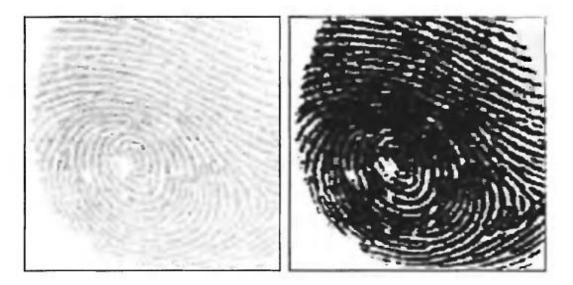

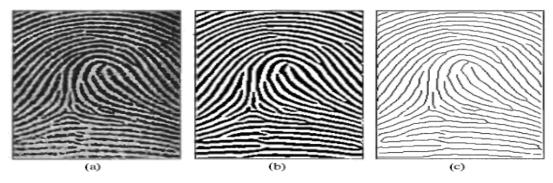

A fingerprint is the reproduction of a fingertip epidermis and is produced when a finger is pressed against a smooth surface. The most evident structural characteristic of a fingerprint is a pattern of interleaved ridges and valleys; in a fingerprint image (Figure 3.1), ridges (also called ridge lines) are dark whereas valleys are bright (Maltoni, Maio, Jain, & Prabhakar, 2003). The size of the ridges vary in width from 100  $\mu$ m, for very thin ridges, to 300  $\mu$ m for thick ridges. Generally, the period of a ridge/valley cycle is about 500  $\mu$ m (Stosz, & Alyea, 1994). Injuries such as burns or cuts do not affect the underlying ridge structure, and the original pattern is duplicated when the new skin grows.

Figure 3.1 Ridges and valleys on a fingerprint image.

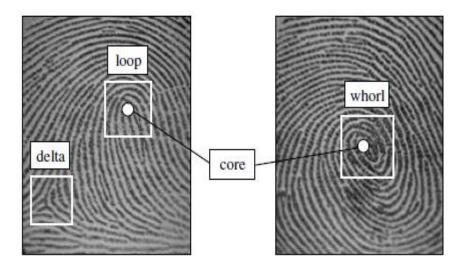

In fingerprint, ridges and valleys often run in parallel. Sometimes, ridges and valleys bifurcate or terminate. If fingerprint is analyzed at the global level, the fingerprint pattern exhibits one or more regions where the ridge lines assume distinctive shapes. These regions are called singularities or singular regions and they can be classified at major and local levels. When major level discussed, it can be

seen that, singular regions may be classified into three typologies: loop, delta, and whorl. Singular regions of a fingerprint belonging to loop, delta, and whorl types are characterized by  $\cap$ ,  $\Delta$ , and O shapes, respectively. Figure 3.2 (Maltoni, Maio, Jain, & Prabhakar, 2003) shows that major singular regions. This figure also shows that the center point of the fingerprint or formerly called core.

Figure 3.2 Singular regions and core points in fingerprint images.

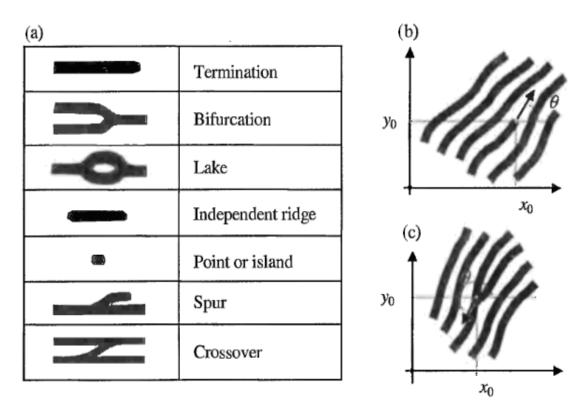

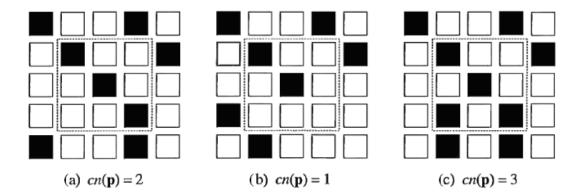

When fingerprint patterns discussed in local level, other important features, called minutiae can be found. Minutia means small detail; in the context of fingerprints, it refers to various ways that the ridges can be discontinuous and for example, a ridge can suddenly come to an end (termination), or can divide into two ridges (bifurcation) (Maltoni, Maio, Jain, & Prabhakar, 2003). Figure 3.3.(a) shows that the most common minutia types such as termination, bifurcation, lake or crossover.

These minutiae types are commonly used for fingerprint recognition. The American National Standards Institute (ANSI) proposed a minutiae taxonomy method based on four classes. These classes are terminations, bifurcations, trifurcations (or crossovers), and undetermined. But, the FBI minutiae-coordinate model considers only terminations and bifurcations: each minutia is denoted by its class, the x- and y-coordinates and the angle between the tangent to the ridge line at the minutia position and the horizontal axis (Figure. 3.3.(b) and 3.3.(c)) (Wegstein, 1982).

Figure 3.3 a) The most common minutiae types; b) Termination minutia :  $[\mathbf{x}_0, \mathbf{y}_0]$  are the minutia coordinates;  $\theta$  is the angle that the minutia tangent forms with the horizontal axis; c) A bifurcation minutia;  $\theta$  is now defined by means of the termination minutia corresponding to the original bifurcation that exists in the negative image (Maltoni, Maio, Jain, & Prabhakar, 2003).

#### 3.2 Fingerprint Image Processing and Feature Extraction

Most of the fingerprint recognition and classification algorithms require a feature extraction stage for identifying remarkable features. The features extracted from fingerprint images often have a direct physical counterpart such as singularities or minutiae, but sometimes they are not directly related to any physical traits such as local orientation image or filter responses. These features may be used directly for matching or an intermediate step for the derivation of other features. For example, some preprocessing and enhancement steps are often performed to simplify the task of minutiae extraction (Maltoni, Maio, Jain, & Prabhakar, 2003).

A fingerprint image, I, is often represented as a two-dimensional surface. When I be a gray-scale fingerprint image with g gray-levels, bright pixels associated with with gray-levels close to g-1 and dark pixels associated with gray-levels close to 0.

#### 3.3 Estimation of Local Ridge Orientation

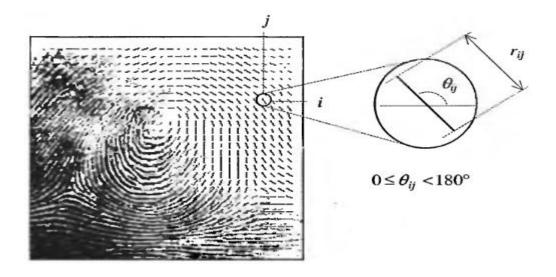

Let [x, y] be a generic pixel in a fingerprint image. The local ridge orientation at [x, y] is the angle  $\theta_{xy}$  that the fingerprint ridges, crossing through an arbitrary small neighborhood centered at [x, y], form with the horizontal axis (Maltoni, Maio, Jain, & Prabhakar, 2003).

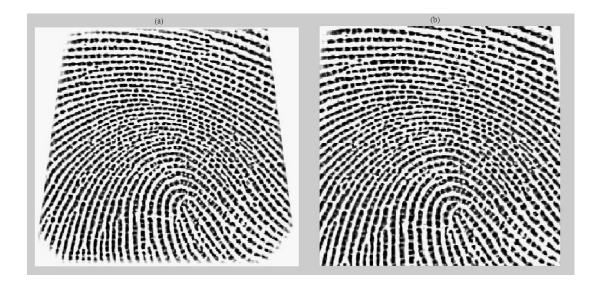

Instead of computing local ridge orientation at each pixel, most of the fingerprint processing and feature extraction methods estimate the local ridge orientation at discrete positions such as local windows. The size of the local windows can be varied depending on the application. The fingerprint orientation image is a matrix D whose elements encode the local orientation of the fingerprint ridges. Figure 3.4 shows the orientation of a fingerprint image (Maltoni, Maio, Jain, & Prabhakar, 2003). Note that each element  $\theta_{ij}$  shows that the orientation of each window. An additional value  $r_{ij}$  is often associated with each element  $\theta_{ij}$  to denote the reliability of the orientation. The simplest and most natural approach for extracting local ridge orientation on a fingerprint image is based on computation of gradients.

Figure 3.4 A fingerprint image faded into the corresponding orientation image computed over a 16 x 16 local windows. Each element denotes the local orientation of the fingerprint ridges,  $\theta_{ij}$ ; the element length is proportional to its reliability,  $r_{ij}$ .

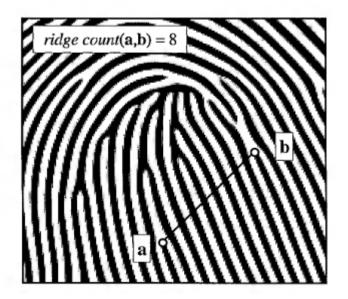

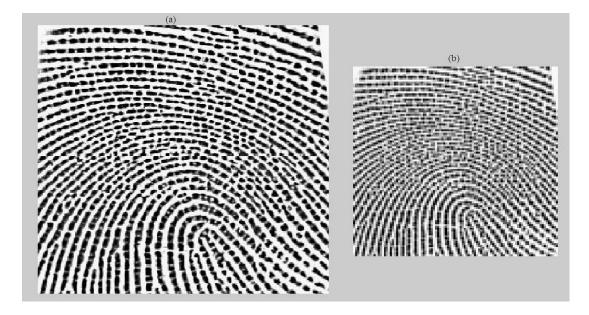

#### 3.4 Estimation of Local Ridge Frequency

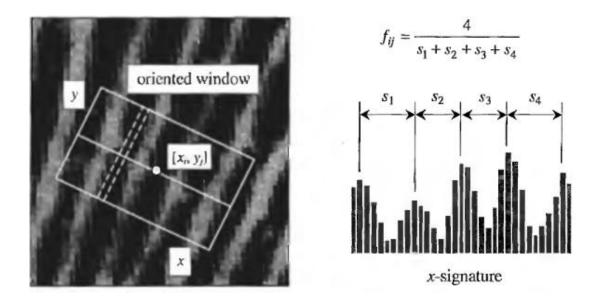

The local ridge frequency (or density)  $f_{xy}$  at point [x, y] is the inverse of the number of ridges per unit length along a hypothetical segment centered at [x, y] and orthogonal to the local ridge orientation  $\theta_{xy}$  (Maltoni, Maio, Jain, & Prabhakar, 2003). A frequency image *F* can be defined if the frequency is estimated at discrete positions and arranged into a matrix. First, 32 x 16 oriented window centered at  $[x_i, y_j]$  is defined. Then the x-signature of the gray-levels is obtained by accumulating, for each column *x*, the gray-levels of the corresponding pixels in the oriented window. This kind of averaging makes the gray-level profile more smoother and prevents ridge peaks.  $f_{ij}$  is determined as the inverse of the average distance between two consecutive peaks of the x-signature. Figure 3.5 shows the estimation of local ridge frequency.

Figure 3.5 Estimation of local ridge frequency. An oriented window centered at  $[x_i, y_j]$ . The dashed lines show the pixels whose gray-levels are accumulated for a given column of the x-signature. The x-signature on the right clearly exhibits five peaks; the four distances between consecutive peaks are averaged to determine the local ridge frequency (Maltoni, Maio, Jain, & Prabhakar, 2003).

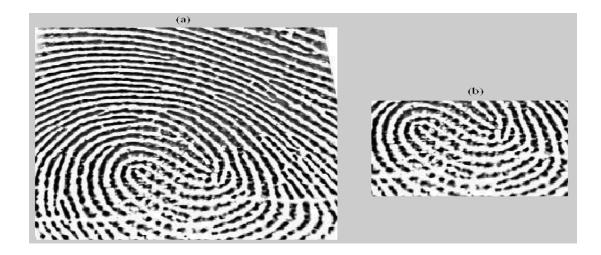

#### 3.5 Singularity and Core Detection

Most of the approaches proposed in the literature for singularity detection operate on the orientation of the fingerprint image. Poincarè index method is the most common method used for detecting singularities and core on a fingerprint pattern. This method is summarized in the following section.

#### 3.5.1 Poincarè Index Method

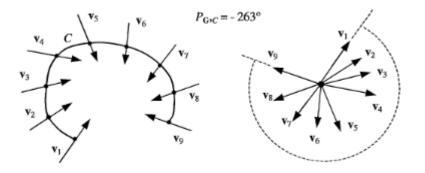

Define G is a vector field and C be a curve in G; then the Poincarè index  $P_{G,C}$  is defined as the total rotation of the vectors of G along curve C (Figure 3.6).

Figure 3.6 The Poincarè index computed over a curve *C* immersed in vector field *G* (Maltoni, Maio, Jain, & Prabhakar, 2003).

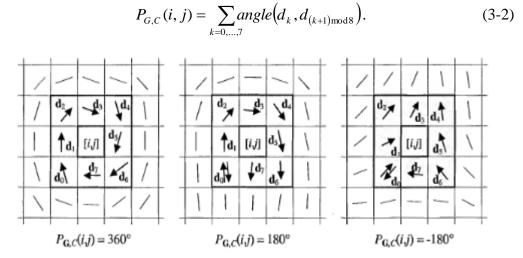

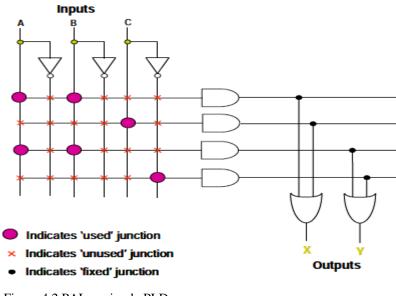

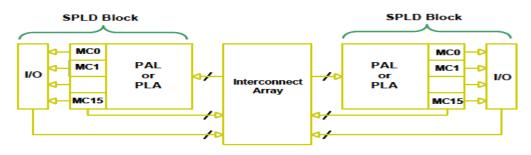

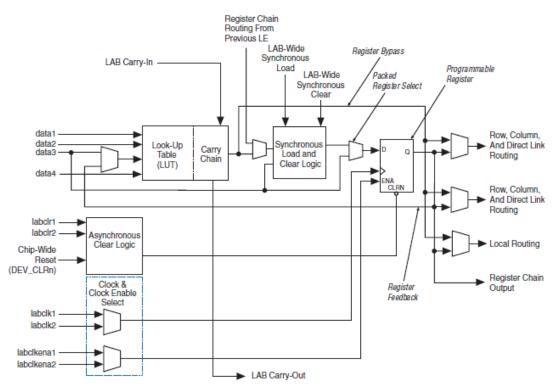

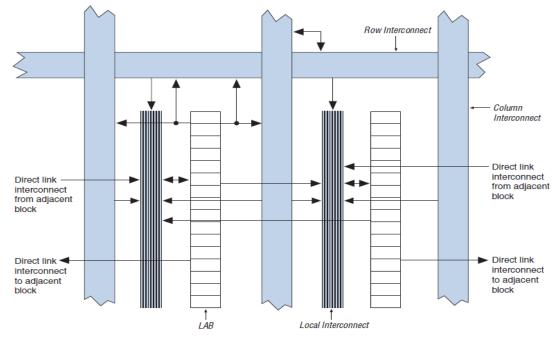

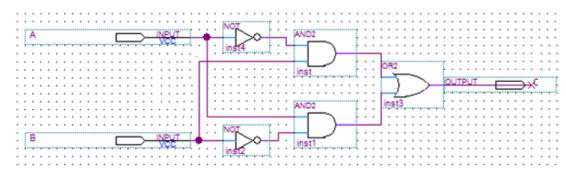

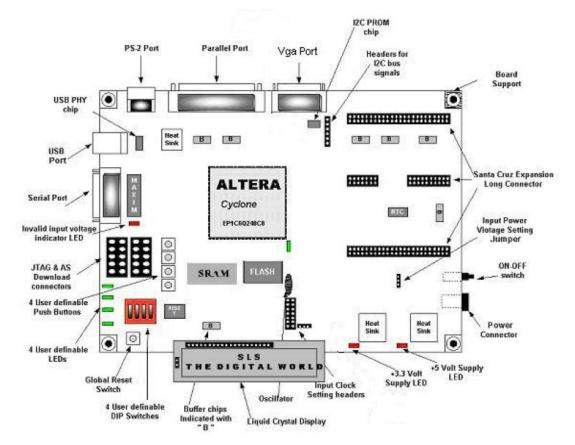

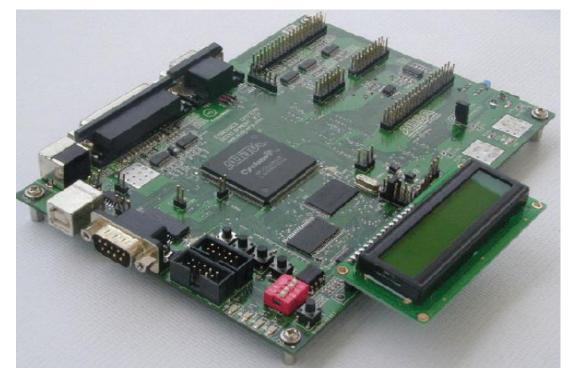

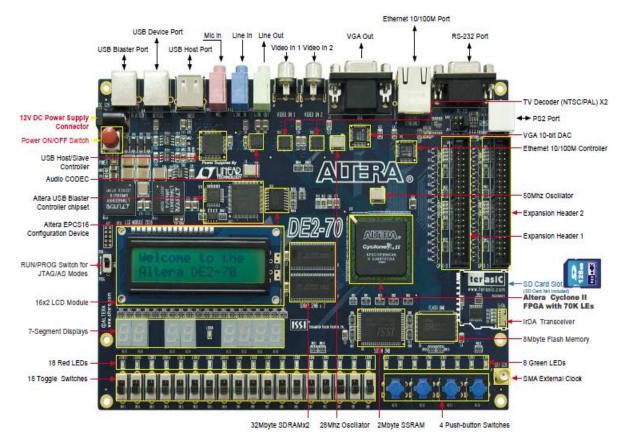

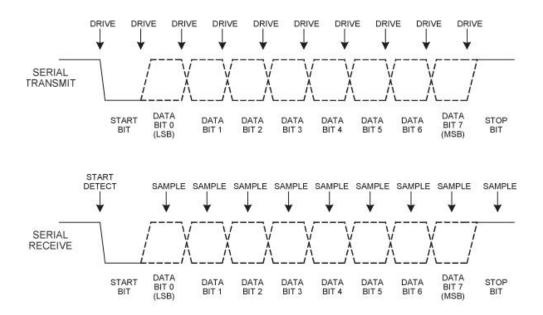

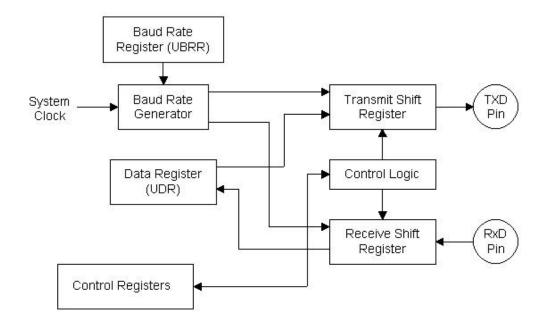

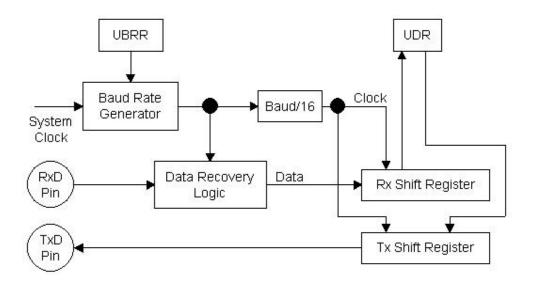

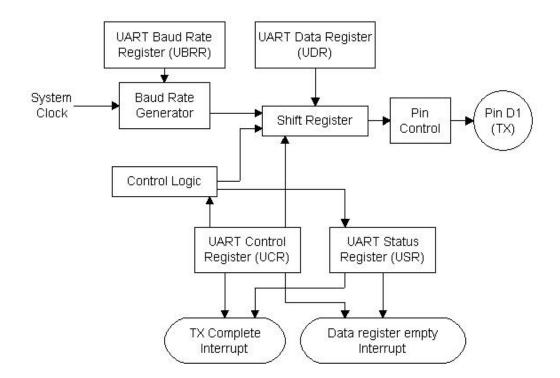

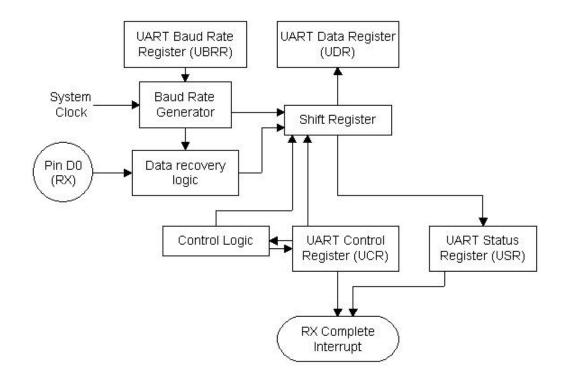

Let *G* be the field associated with a fingerprint orientation image *D* and let [i, j] be the position of the element  $\theta_{ij}$  in the orientation image; then the Poincarè index  $P_{G,C}(i, j)$  at [i, j] is computed by first taking the curve *C* is a closed path defined as an ordered sequence of some elements of *D*. Usually the element [i, j] of *D* is internal point.  $P_{G,C}(i, j)$  is computed by algebraically summing the orientation differences between adjacent elements of curve *C*. Summing orientation differences require a direction to be associated at each orientation. For solving this problem, the direction of the first element is randomly selected and the direction of the other elements is found by assigning the closest direction to that of the previous element to each successive element. On closed curves, the Poincarè index assumes only one of the discrete values:  $0^{\circ}$ ,  $\pm 180^{\circ}$ , and  $\pm 360^{\circ}$ . Singularities on a fingerprint image are defined in Eq. (2-1).